# WARSAW UNIVERSITY OF TECHNOLOGY

DISCIPLINE OF SCIENCE - DISCIPLINE OF AUTOMATION,

ELECTRONICS, ELECTRICAL ENGINEERING AND SPACE

TECHNOLOGIES

FIELD OF SCIENCE - ENGINEERING AND TECHNOLOGY

# Ph.D. Thesis

Alvaro Andres Carreno Henriquez, M.Sc.

Control of a Hybrid Transformer to Improve the Power Quality in a Distribution Network

Supervisors Prof. dr hab. inż. Mariusz Malinowski Prof. dr inż. Marcelo Perez

WARSAW 2024

# UNIVERSIDAD TÉCNICA FEDERICO SANTA MARÍA DEPARTMENT OF ELECTRONICS ENGINEERING VALPARAISO - CHILE

# Ph.D. Thesis Control of a Hybrid Transformer to Improve the Power Quality in a Distribution Network

#### Alvaro Andres Carreno Henriquez, M.Sc.

Doctorate program

Doctorate in Electronic Engineering

Supervisors: Dr. Marcelo Perez

Dr. Mariusz Malinowski

VALPARAISO 2024

# **ABSTRACT**

Conventional distribution transformers are not capable of dealing with modern and future power systems in which features such as renewable energy systems integration, energy storage, power quality improvement, and bidirectional power flow management are required. To achieve these goals, alternatives to the conventional distribution transformer, such as the Solid-State Transformer (SST), have been proposed. Nonetheless, the SST is far from being a real solution due to reliability and low short-circuit power issues. These problems can be tackled by employing hybrid solutions, such as the Hybrid Distribution Transformer (HDT).

Most HDT configurations comprise a series converter and a parallel converter, where the parallel converter is typically integrated into the main transformer via an auxiliary winding, and the series converter is connected to the secondary side of the transformer. In these configurations, the main transformer is unprotected from the grid voltage and load current disturbances. Even while using the parallel converter to compensate for the nonlinear load currents, and provide sinusoidal currents on the medium voltage side, nonlinear currents circulate through the secondary winding of the transformer. Moreover, the nonlinear currents injected by the parallel converter flow through the auxiliary winding of the main transformer. On the other side, under grid voltage disturbances, the series converter compensates for the voltage disturbances providing a sinusoidal voltage to the load. Nonetheless, polluted and unbalanced voltages are still applied to the transformer terminal. These operating conditions can reduce the lifetime of the main transformer, potentially damaging it.

To address the issues presented in most HDTs, this work proposes an HDT

configuration in which the series converter is connected to the primary side winding, and the parallel converter is connected directly to the secondary side winding. This configuration improves the power quality of the transformer by reducing the THD of the current and the voltage to its terminals while at the same time providing a regulated voltage to the loads. Moreover, retrofitting of the main transformer is potentially allowed.

A discrete-time state feedback controller is designed for the parallel and series converters, in which the main objectives are the improvement of the power quality on the transformer, as well as providing nominal voltage to the loads. The HDT operates under uncertain grid and load conditions. Therefore, in order to preserve the stability of the system, the control algorithm is based on the Linear Quadratic Regulator (LQR). Although the proposed HDT improves the power quality of the system, it requires a Circulating Active Power Flow (CAPF) to work properly. Unless the voltage controller and current controller are degraded or the structure of the HDT is modified, the CAPF is unavoidable. Therefore, part of this work is devoted to its analysis, its impact on the operating conditions, and the efficiency of the HDT.

The main transformer of the HDT can generate inrush currents during and after grid voltage sags or swells. To conclude the thesis and as a proof of concept, the series converter controller is extended and used to regulate the magnetic flux of the main transformer and avoid high-amplitude currents that could jeopardize the grid operation.

*Keywords*—hybrid distribution transformer, efficiency, power quality, discrete-time control, circulating active power flow, voltage and current distortion.

# **STRESZCZENIE**

Coraz więcej badań dotyczy integracji systemów energii odnawialnej, systemów magazynowania energii oraz wydajnych metod konwersji i poprawy jej jakości. Aby osiągnąć te cele, zaproponowano alternatywy dla konwencjonalnego transformatora dystrybucyjnego transformator półprzewodnikowy (SST), aby poradzić sobie z trudnymi warunkami narzuconymi przez rzeczywiste i nowoczesne systemy elektroenergetyczne. Niemniej jednak, SST jest daleki od bycia rzeczywistym i praktycznym rozwiązaniem ze względu na słabą niezawodność i niską moc zwarciową. Problemy te można rozwiązać poprzez zastosowanie rozwiązań hybrydowych, takich jak hybrydowy transformator dystrybucyjny (HDT).

Większość konfiguracji HDT składa się z przekształtnika szeregowego i przekształtnika równoległego, przy czym przekształtnik równoległy jest zwykle zintegrowany z głównym transformatorem dystrybucyjnym za pośrednictwem uzwojenia pomocniczego, a przekształtnik szeregowy jest podłączony do strony wtórnej tego transformatora. W takich konfiguracjach główny transformator dystrybucyjny nie jest chroniony przed zaburzeniami napięcia sieciowego i prądu obciążenia. Nawet podczas korzystania z przekształtnika równoległego w celu kompensacji nieliniowych prądów obciążenia i zapewnienia sinusoidalnych prądów po stronie średniego napięcia, prądy nieliniowe cyrkulują przez uzwojenie wtórne transformatora. Ponadto prądy nieliniowe wstrzykiwane przez przekształtnik równoległy przepływają przez uzwojenie pomocnicze głównego transformatora dystrybucyjnego. Z drugiej strony, w przypadku zaburzeń napięcia sieciowego, przekształtnik szeregowy kompensuje je, dostarczając do obciążenia napięcie sinusoidalne. Niemniej jednak, zaburzone i asymetryczne napięcia są nadal podawane na

zaciski wejściowe transformatora. Takie warunki pracy mogą skrócić żywotność głównego transformatora, potencjalnie powodując jego uszkodzenie w dalszej perspektywie.

Aby rozwiązać problemy występujące w większości HDT, w niniejszej pracy zaproponowano konfigurację HDT, w której przekształtnik szeregowy jest podłączony do strony pierwotnej, a przekształtnik równoległy jest podłączony bezpośrednio do uzwojenia strony wtórnej transformatora dystrybucyjnego. Taka konfiguracja poprawia jakość zasilania transformatora, zmniejszając THD prądu i napięcia na jego zaciskach, jednocześnie zapewniając regulowane napięcie dla odbiorników. Co więcej, taka modernizacja głównego transformatora dystrybucyjnego jest łatwa do realizacji.

Zaprojektowano dyskretny regulator ze sprzężeniem zwrotnym dla przekształtników równoległego i szeregowego, w których głównym celem jest poprawa jakości energii w transformatorze, a także zapewnienie nominalnego napięcia dla odbiorników. HDT działa w niepewnych warunkach sieci i obciążenia. Dlatego też, w celu zachowania stabilności systemu, algorytm sterowania oparty jest na liniowym regulatorze kwadratowym (LQR). Chociaż proponowany HDT poprawia jakość zasilania systemu, do prawidłowego działania wymaga on cyrkulacyjnego przepływu mocy czynnej (CAPF). O ile w regulacji napięcia i prądu nie zostaną dopuszczone warunki nienominalne lub struktura HDT nie zostanie zmodyfikowana, CAPF jest nieunikniony. Dlatego też część niniejszej pracy poświęcona jest jego analizie, wpływowi na warunki pracy i wydajność HDT.

Podsumowując, główny transformator HDT może generować prądy rozruchowe podczas i po spadkach lub wzrostach napięcia w sieci. W związku z tym jako dowód słuszności koncepcji, sterownie przekształtnika szeregowego zostało rozszerzone i wykorzystane do regulacji strumienia magnetycznego głównego transformatora dystrybucyjnego w celu uniknięcia prądów o wysokiej amplitudzie, które mogłyby zagrozić poprawnemu działaniu sieci elektroenergetycznej.

*Słowa kluczowe*—hybrydowy transformator dystrybucyjny, sprawność, jakość energii, sterowanie dyskretne, cyrkulacyjny przepływ mocy czynnej, zniekształcenia napięcia i prądu.

### **RESUMEN**

Los transformadores de distribución convencionales no son capaces de tratar con los sistemas de potencia modernos y del futuro, en los que se requieren la integración de sistemas de energía renovables, almacenamiento de energía, mejoramiento de la calidad de la energía, y manejo de flujos de potencia bidireccionales. Para alcanzar estas metas, se han propuesto alternativas al transformador de distribución convencional que permitan manejar las desafiantes condiciones impuestas por los sistemas de potencia actuales y modernos. Una de estas alternativas es el transformador de estado sólido (SST). Sin embargo, el SST aún está lejos de ser aplicable en soluciones reales debido principalmente a problemas relacionados con la confiabilidad y baja potencia de corto circuito. Estos problemas pueden ser abordados empleando soluciones híbridas, tal como el transformador de distribución híbrido (HDT).

La mayoría de las configuraciones de HDTs constan de un convertidor conectado en serie, y otro convertidor conectado en paralelo. El convertidor paralelo es típicamente conectado a un devanado auxiliar, mientras que el convertidor serie es conectado en el secundario del transformador principal. En estas configuraciones, el transformador principal está desprotegido de las perturbaciones del voltaje de la red y de las corrientes de carga. Incluso cuando el convertidor paralelo es utilizado para compensar y mejorar las corrientes que circulan en la red de medio voltaje, las corrientes no lineales de la carga fluyen a través del transformador, como también lo hacen las corrientes de compensación del convertidor paralelo. Por otro lado, al operar bajo perturbaciones de la red de medio voltaje, el convertidor serie compensa el efecto de las perturbaciones en la carga, entregando un voltaje sinusoidal y nominal. Sin embargo, los terminales

del transformador principal están sujetos al voltaje de la red, el cual puede estar distorsionado y desbalanceado. Estas condiciones de operación pueden reducir la vida útil del transformador principal, dañándolo potencialmente.

Para tratar los problemas presentados en la mayoría de HDTs, este trabajo propone un HDT, en el que el convertidor serie se conecta al primario, y el convertidor paralelo se conecta al secundario del transformador principal. Esta configuración permite mejorar la calidad de la energía en el transformador, mejorando el THD de la corriente y voltaje en sus terminales, mientras que al mismo tiempo provee un voltaje regulado a las cargas. Además, la conversión de los transformadores de distribución en operación a HDT es potencialmente posible.

Un controlador de realimentación de variables de estado en tiempo discreto es diseñado para el convertidor paralelo y serie, en el que el principal diseño de control es el mejoramiento de la calidad de la energía en el transformador principal, como también la regulación del voltaje de las cargas. Debido a su naturaleza, el HDT opera bajo condiciones de red y carga inciertas. Por lo tanto, para preservar la estabilidad del sistema, el algoritmo de control es diseñado empleado un controlador cuadrático lineal (LQR). Aunque el HDT mejora la calidad de energía del sistema, requiere un flujo de potencia activa circulante (CAPF) para operar correctamente. A menos que el controlador de voltaje y corrientes sean degradados, o que la estructura del HDT sea modificada, el CAPF es inevitable. Por lo tanto, parte de este trabajo es enfocada a analizar el impacto del CAPF en las condiciones de operación y eficiencia del HDT.

El transformador principal del HDT puede generar corrientes inrush mientras y luego de haber sido expuesto a caídas y sobre tensiones. Para concluir la tesis y como prueba de concepto, el controlador del convertidor series es extendido y utilizado para regular el flujo magnético del transformador, y de esta forma evitar corrientes de alta amplitud que puedan afectar la correcta operación del sistema.

Palabras clave—Transformador de distribución híbrido, eficiencia, calidad de la energía, control en tiempo discreto, flujo de potencia activa circulante, distorsión de voltage y corriente.

# **ACKNOWLEDGMENTS**

First of all, I would like to thank my parents Patricia and Carlos, and my brother Marcel. I feel your support and love constantly. I also would like to thank Anna. Without your support, love, and patience, it would not have been possible to conclude this work.

I would like to thank Professor Marcelo Pérez for giving me his invaluable guidance and support during the development of this thesis. Also, I would like to thank Professor Mariusz Malinowski, who received me in Poland, supported me, and inspired me during the Ph.D. I appreciate having the opportunity to work with both of you.

Finally, I want to thank Professor Marek Jasiński and the research group of GE007B: Tomasz Święchowicz, Sebastian Styński, Tomasz Gajowik, Adam Milczarek, Radek Kot, Cezary Soból, Luis Martinez, Kamil Możdżyński, and Serafin Bachman. Thanks for all the help in the laboratory and for making the time abroad much easier.

# **CONTENTS**

| A            | bstra                     | ct                                            | V                    |

|--------------|---------------------------|-----------------------------------------------|----------------------|

| St           | reszo                     | zenie                                         | vii                  |

| $\mathbf{R}$ | esum                      | e <b>n</b>                                    | ix                   |

| $\mathbf{A}$ | cknov                     | vledgments                                    | xi                   |

| $\mathbf{C}$ | onter                     | ${f ts}$                                      | xiii                 |

| Li           | st of                     | Figures                                       | xvii                 |

| Li           | st of                     | Tables                                        | xxi                  |

| $\mathbf{A}$ | crony                     | ms                                            | xxiii                |

| 1            | Intr<br>1.1<br>1.2<br>1.3 | The conventional and modern distribution grid | . 5                  |

|              | 1.0                       | 1.3.1 Self-supported HDTs                     | . 8<br>. 10<br>. 12  |

|              | 1.4                       | Power converter location effects              | . 15<br>. 15<br>. 17 |

|              | 1.5                       | Applications of HDTs                          |                      |

|          |                   | 1.5.1 Distribution transformer inrush current mitigation                     | 19        |

|----------|-------------------|------------------------------------------------------------------------------|-----------|

|          |                   | 1.5.2 Distribution transformer additional capacity                           | 21        |

|          |                   | 1.5.3 HDTs to provide virtual inertia                                        | 21        |

|          |                   | 1.5.4 Renewable energy systems and new kind of loads integration             | 21        |

|          |                   | 1.5.5 Decentralized control of an HDT for voltage regulation in active grids | 22        |

|          | 1.6               | Thesis motivation                                                            | 22        |

|          | 1.7               | Formulation of the thesis                                                    | 25        |

|          | 1.8               | Contributions of the author                                                  | 25        |

|          | 1.9               | Outline of the dissertation                                                  | 26        |

|          | 1.10              | Publications generated from the doctoral thesis                              | 26        |

|          |                   | 1.10.1 Journal publications                                                  | 26        |

|          |                   | 1.10.2 International conference publications                                 | 27        |

| <b>2</b> | Mod               | del of the HDT                                                               | 29        |

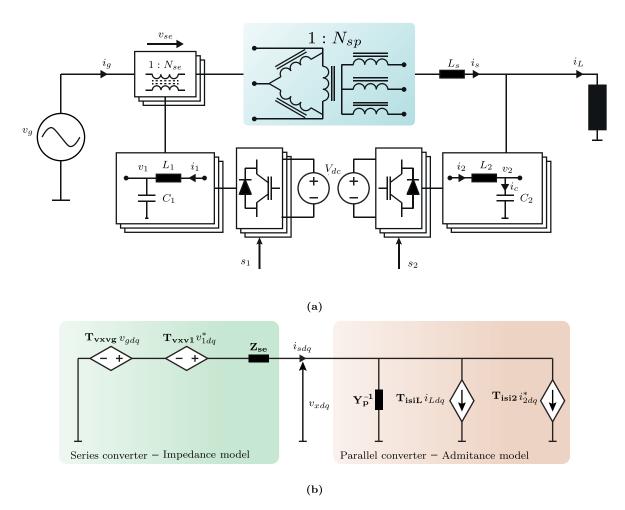

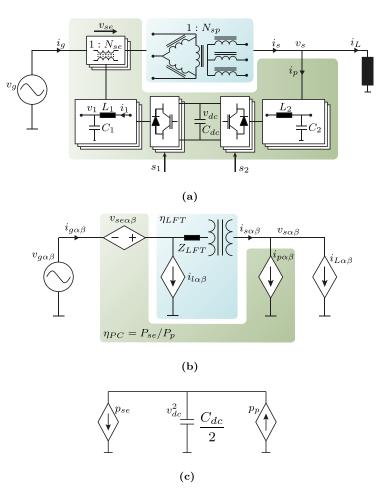

|          | 2.1               | System under study                                                           | 30        |

|          | 2.2               | Series converter model                                                       | 30        |

|          | 2.3               | Parallel converter model                                                     | 34        |

|          |                   | 2.3.1 State-space representation in $\alpha\beta$ coordinates                | 35        |

|          |                   | 2.3.2 State-space representation in $\gamma$ coordinate                      | 37        |

|          |                   | 2.3.3 DC-Link model                                                          | 38        |

|          | 2.4               | Combined AC model                                                            | 39        |

|          | 2.1               | 2.4.1 Series converter - Coupling transformer current                        | 39        |

|          |                   | 2.4.2 Parallel converter - Induced voltage                                   | 41        |

|          |                   | 2.4.3 Combined model                                                         | 43        |

|          |                   | 2.4.4 Open-loop characteristic of the HDT                                    | 45        |

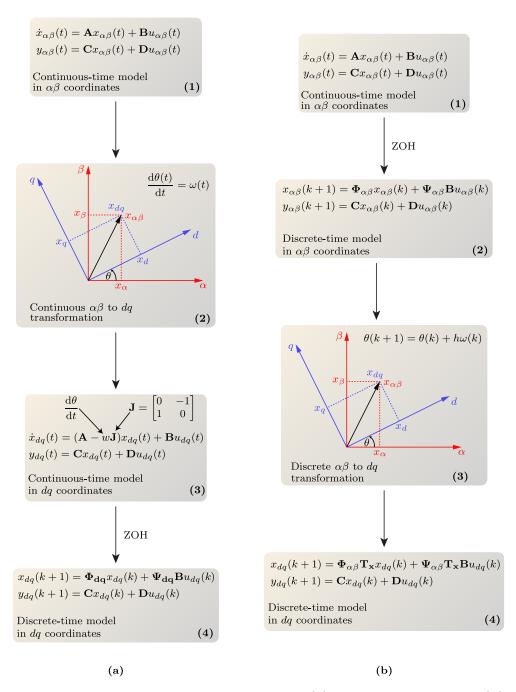

|          | 2.5               | Discrete dq model                                                            | 47        |

|          | $\frac{2.5}{2.6}$ | Conclusion                                                                   | 49        |

|          | 2.0               | Conclusion                                                                   | 49        |

| 3        |                   | ı v                                                                          | <b>51</b> |

|          | 3.1               | Control system in $dq$ coordinates                                           |           |

|          |                   | 3.1.1 Series converter                                                       | 52        |

|          | 0.0               | 3.1.2 Parallel converter                                                     | 54        |

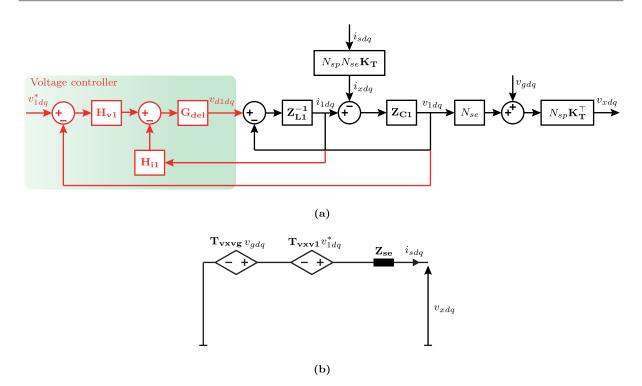

|          | 3.2               | Series converter impedance model                                             | 55        |

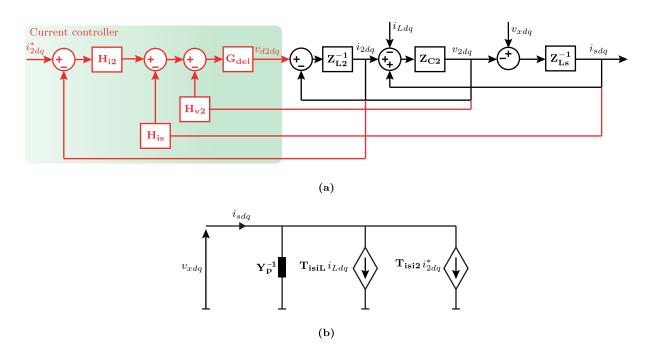

|          | 3.3               | Parallel converter admittance model                                          | 57        |

|          | 3.4               | HDT combined stability                                                       | 59        |

|          | 3.5               | Stability assessment                                                         | 61        |

|          |                   | 3.5.1 Series converter                                                       | 61        |

|          |                   | 3.5.2 Parallel converter                                                     | 62        |

|          |                   | 3.5.3 Combined operation                                                     | 64        |

|          | 3.6               | Experimental results                                                         | 66        |

|          | 3.7               | Conclusion                                                                   | 68        |

| 4        | Circ              | culating Active Power Flow (CAPF) analysis and Efficiency of the             |           |

|          | HD'               | $\Gamma$                                                                     | 69        |

|          | 4.1               | Losses in Distribution Transformers                                          | 72        |

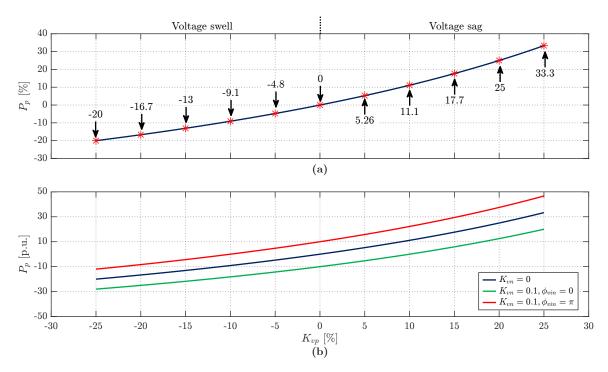

|          | 4.2               | CAPE model                                                                   | 74        |

#### Contents

|   |     | 4.2.1 Comments on $\phi_{vin}$ and CAPF example                  |     |

|---|-----|------------------------------------------------------------------|-----|

|   |     | 4.2.2 HDT efficiency                                             |     |

|   | 4.3 | <i>v</i> 1                                                       | 90  |

|   |     | 11                                                               | 90  |

|   |     | v 1                                                              | 92  |

|   |     | 4.3.3 DC-Link design                                             |     |

|   | 4.4 | Methods to reduce the CAPF                                       |     |

|   |     | 4.4.1 Reactive power injection                                   |     |

|   |     | 4.4.2 Power routing using the DC port                            |     |

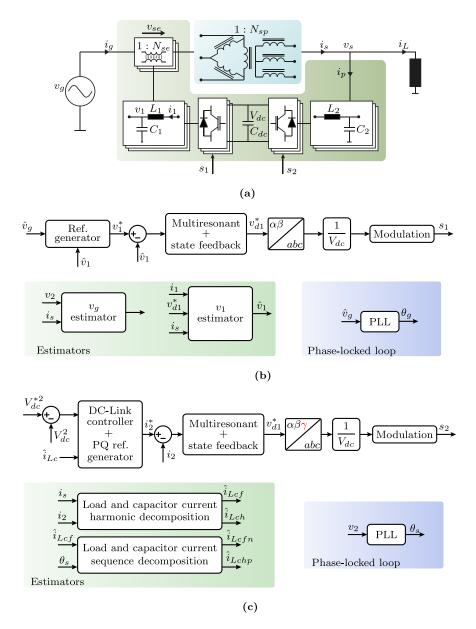

|   | 4.5 | Control of the HDT for CAPF analysis                             |     |

|   |     | 4.5.1 Series converter controller                                |     |

|   |     | 4.5.2 Parallel converter controller                              |     |

|   |     | 4.5.3 Load current filtering                                     |     |

|   | 4.6 | Simulation results                                               |     |

|   | 4.7 | Experimental results                                             |     |

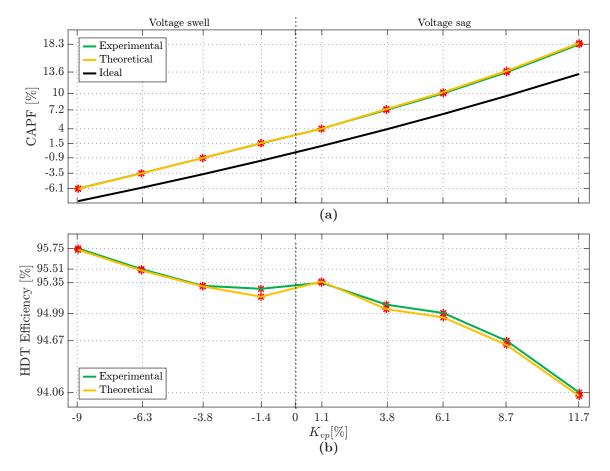

|   |     | 4.7.1 CAPF and efficiency of the HDT                             |     |

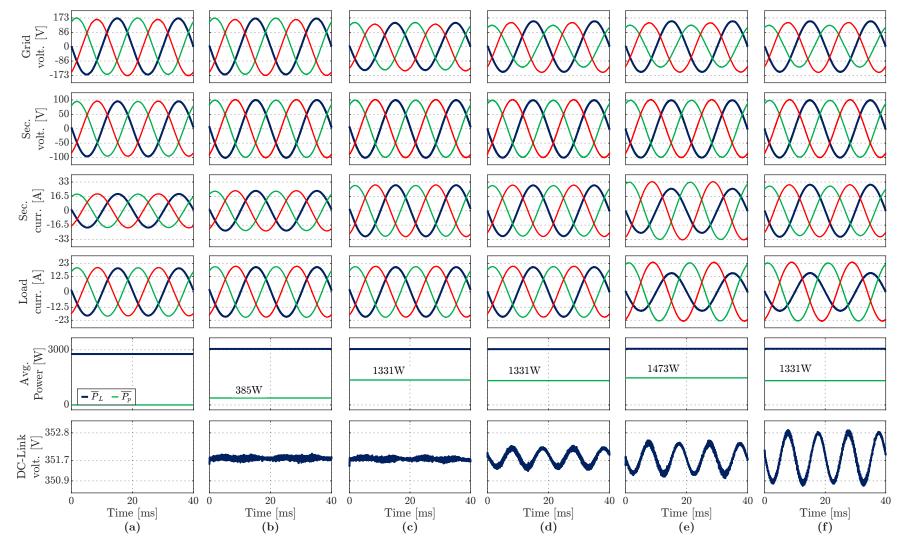

|   |     | 4.7.2 Balanced and unbalanced operation                          |     |

|   |     | 4.7.3 CAPF reduction methods                                     |     |

|   | 4.8 | Conclusions                                                      | .14 |

| 5 | Cor | rol of the HDT to Improve Power Quality 1                        | 15  |

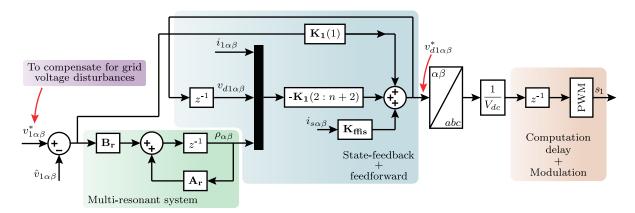

|   | 5.1 | Series converter controller in $\alpha\beta$ coordinates         | _   |

|   | 0.1 | 5.1.1 Discrete model                                             |     |

|   |     | 5.1.2 Capacitor voltage regulator                                |     |

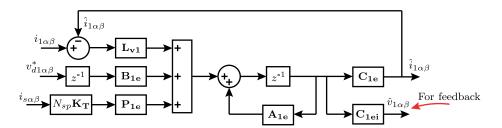

|   |     | 5.1.3 Capacitor voltage observer                                 |     |

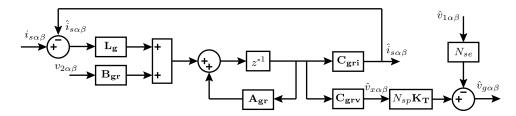

|   |     | 5.1.4 Grid voltage estimator                                     |     |

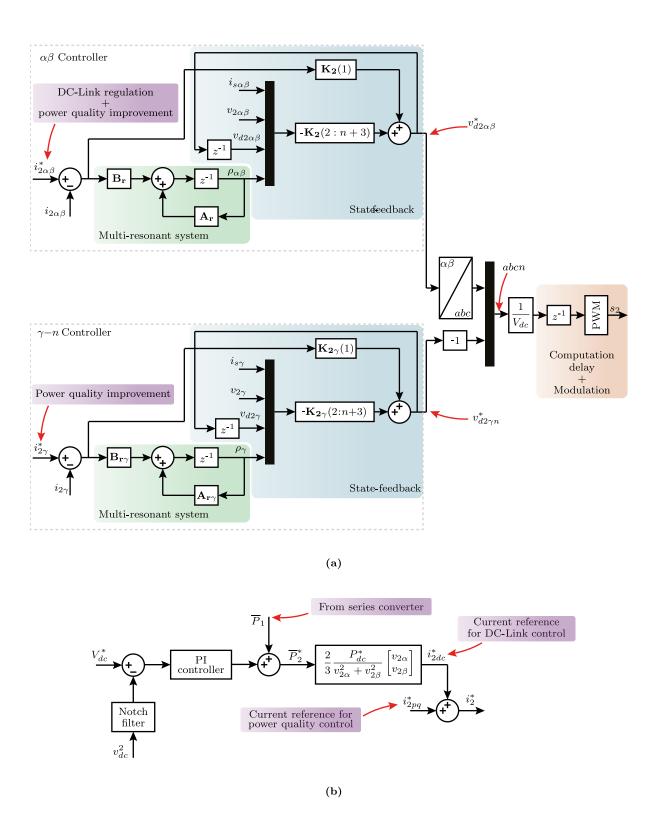

|   | 5.2 | Parallel converter controller in $\alpha\beta\gamma$ coordinates |     |

|   |     | 5.2.1 Discrete model                                             |     |

|   |     | 5.2.2 Current controller                                         |     |

|   |     | 5.2.3 DC-Link controller                                         |     |

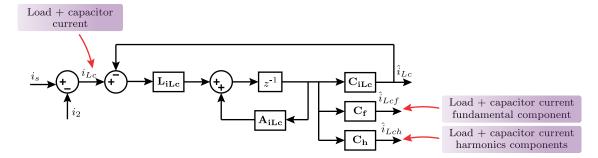

|   |     | 5.2.4 Load current harmonic decomposition                        | 34  |

|   |     | 5.2.5 Load current sequence decomposition                        |     |

|   | 5.3 | Simulation results                                               | 36  |

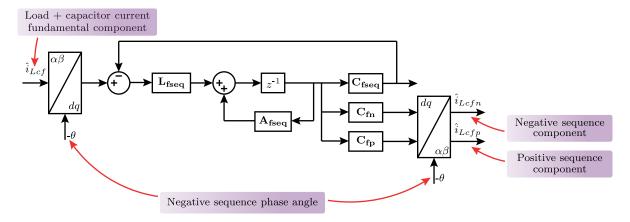

|   |     | 5.3.1 Parameter stability analysis                               |     |

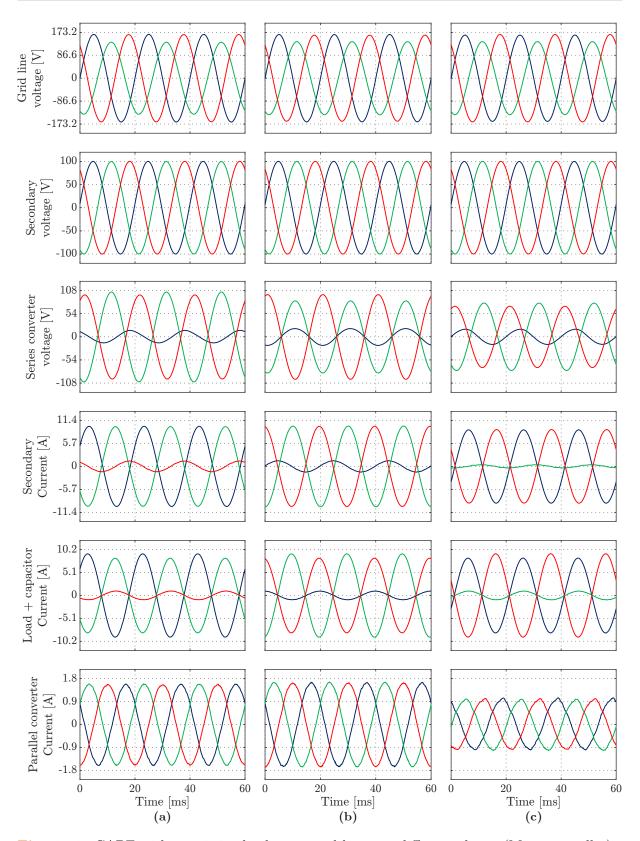

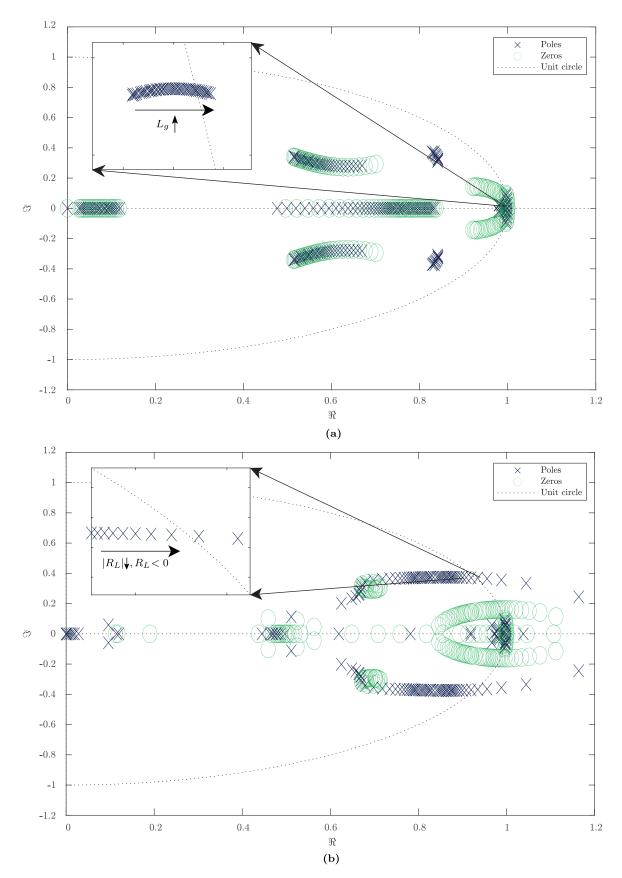

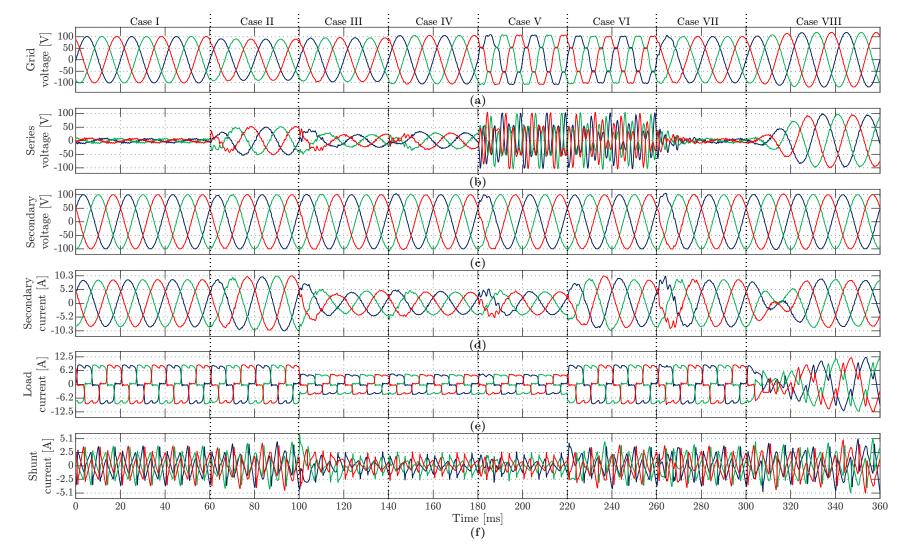

|   |     | 5.3.2 Simulation cases                                           |     |

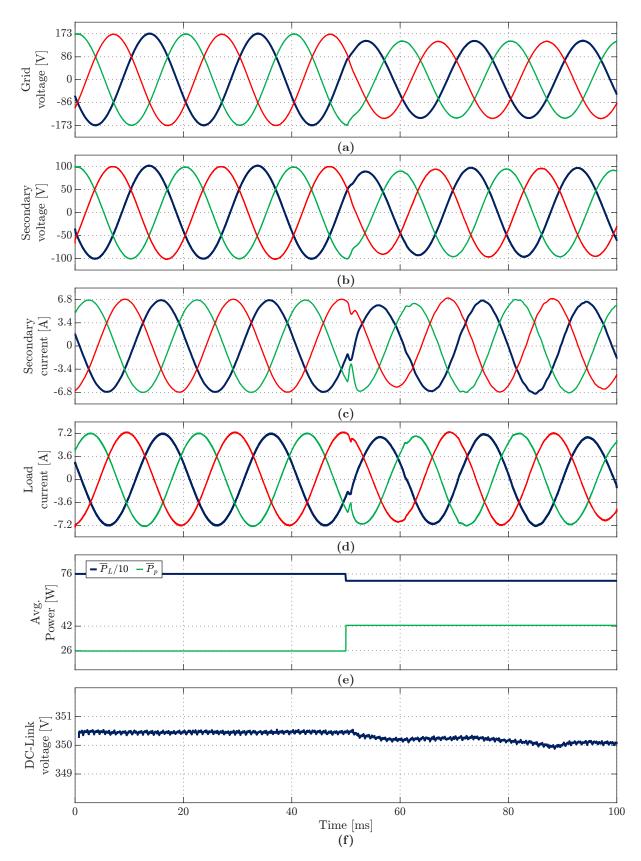

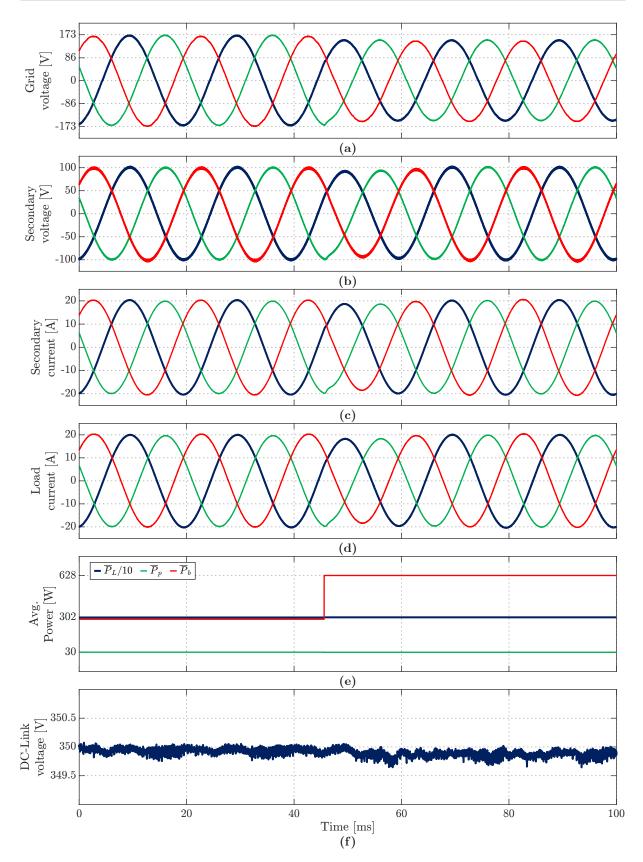

|   | 5.4 | Experimental results                                             | 44  |

|   |     | 5.4.1 3-wire grid                                                |     |

|   |     | 5.4.2 4-wire grid                                                |     |

|   | 5.5 | Conclusion                                                       |     |

| 6 | Pro | of of concept: Flux regulation 1                                 | 61  |

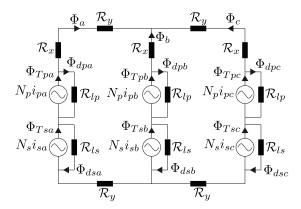

| J | 6.1 | Three-legged distribution transformer magnetic model             |     |

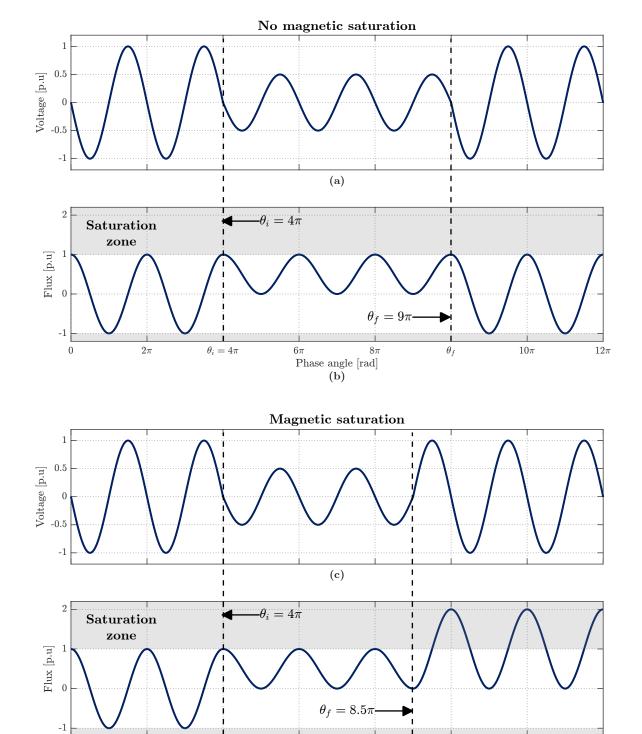

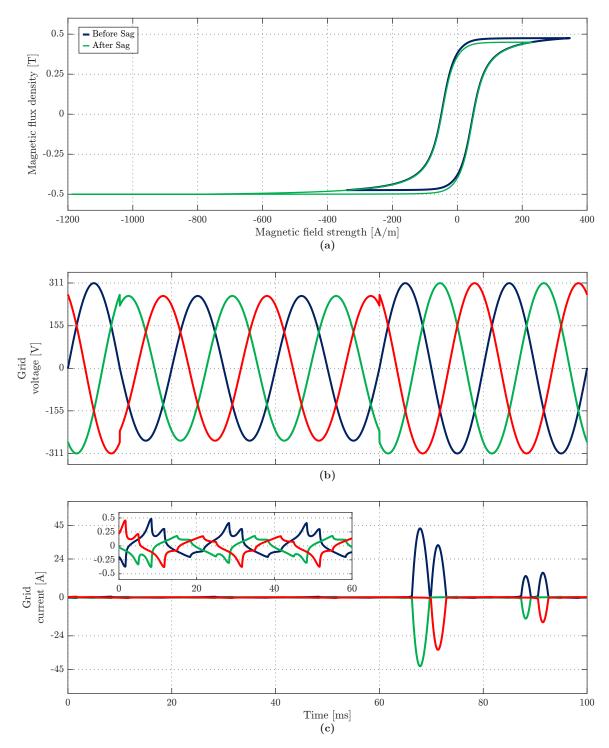

|   | 6.2 | Voltage sags effects                                             |     |

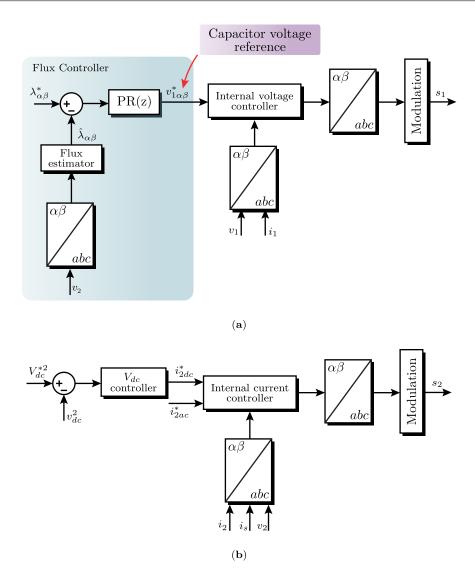

|   | 6.3 | Flux Regulation                                                  |     |

|   | 2.3 | 6.3.1 Internal controllers                                       |     |

|   |     |                                                                  | 68  |

|              |            | Conte                                      | nts              |

|--------------|------------|--------------------------------------------|------------------|

|              | 6.4<br>6.5 | 6.3.3 Flux estimator                       | 70               |

| 7            |            | Elusions 1 Future work                     | <b>75</b><br>.77 |

| $\mathbf{A}$ | A.1        | Ar Quadratic Regulator  Discrete-time case |                  |

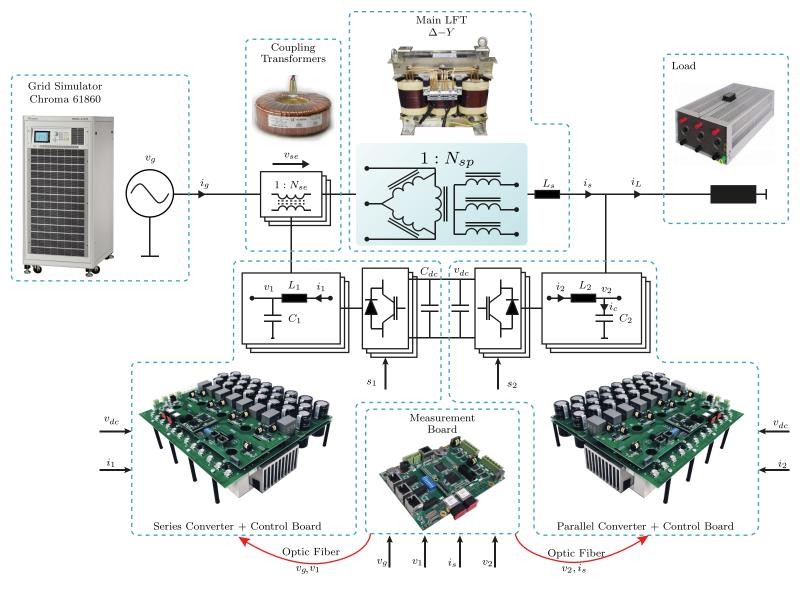

| В            | Exp        | erimental setup 1                          | 83               |

| $\mathbf{C}$ | MV         | to LV simulation 1                         | 89               |

| Bi           | bliog      | raphy 1                                    | 97               |

# LIST OF FIGURES

| 1.1  | Solid-State Transformer concept                     | 4  |

|------|-----------------------------------------------------|----|

| 1.2  | Hybrid Distribution Transformer concept             | 6  |

| 1.3  | Hybrid transformer with bypass switch               | 7  |

| 1.4  | HDT configurations                                  | 9  |

| 1.5  | Integrated magnetics HDT                            | 13 |

| 1.6  | Other HDT configurations                            | 14 |

| 1.7  | Parallel and series converter locations             | 16 |

| 1.8  | Active power flow scenarios                         | 18 |

| 1.9  | Ancillary services provided by HDTs                 | 20 |

| 1.10 | Qualitative comparison of HDT configurations        | 23 |

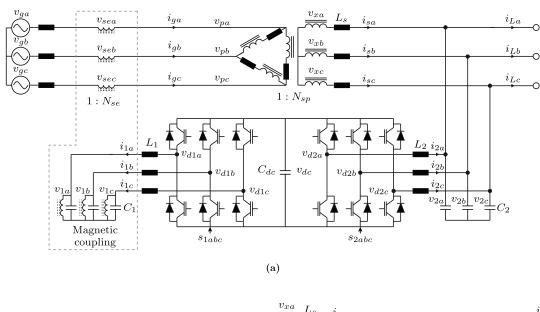

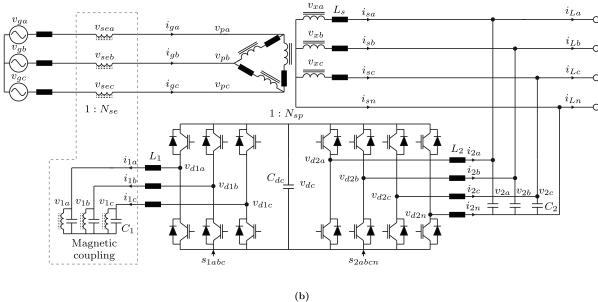

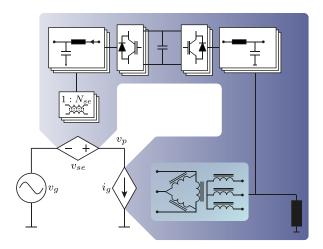

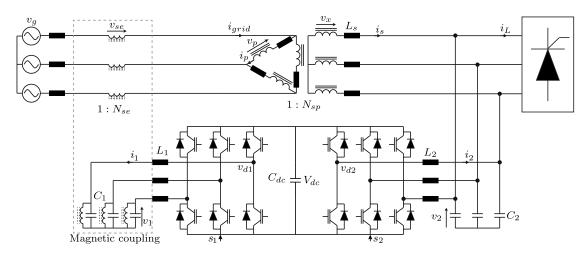

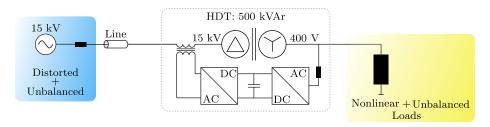

| 2.1  | Proposed HDT configuration                          | 31 |

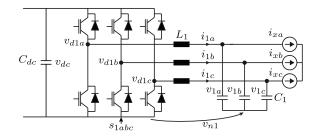

| 2.2  | Series converter with output $LC$ filter            | 32 |

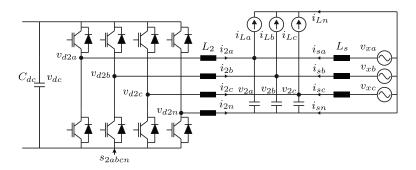

| 2.3  | Parallel converter of the HDT                       | 35 |

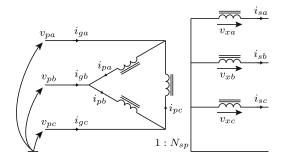

| 2.4  | LFT winding configuration and associated variables  | 40 |

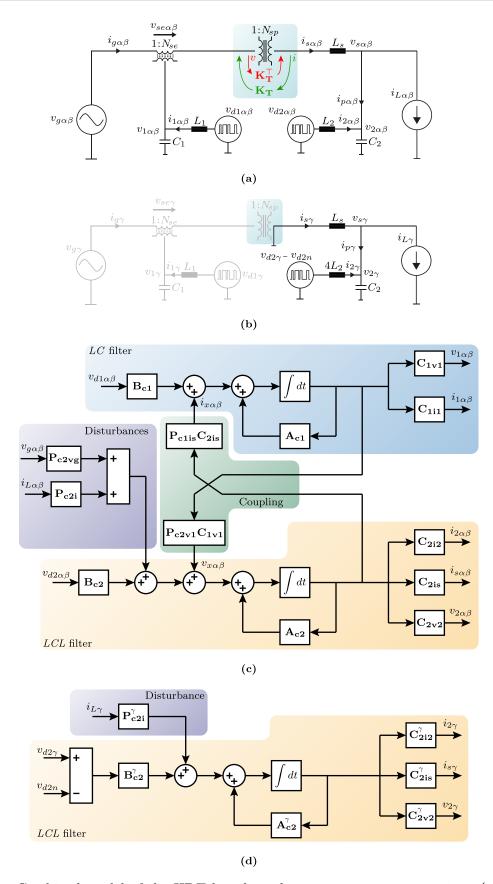

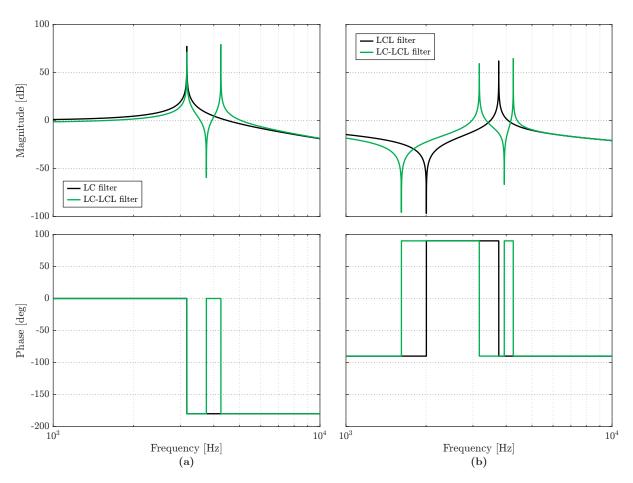

| 2.5  | Combined model of the HDT                           | 44 |

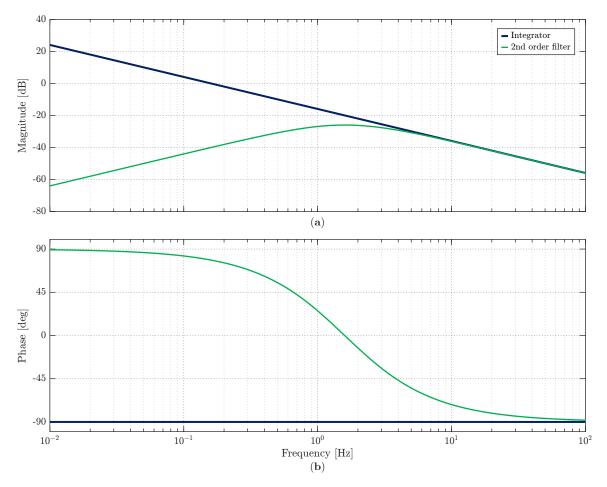

| 2.6  | Bode diagrams comparison                            | 46 |

| 2.7  | Discrete-time $\alpha\beta$ to $dq$ transformation  | 48 |

| 3.1  | HDT controller for balanced operation               | 53 |

| 3.2  | Series converter model                              | 55 |

| 3.3  | Parallel converter model                            | 57 |

| 3.4  | Combined model                                      | 60 |

| 3.5  | Series converter - Nyquist plot                     | 63 |

| 3.6  | Parallel converter - Nyquist plot                   | 64 |

| 3.7  | Series and parallel converter - Frequiency response | 65 |

| 3.8  | 1 , 1                                               | 65 |

| 3.9  | Experimental result - Balanced voltage sag          | 67 |

|      |                                                     |    |

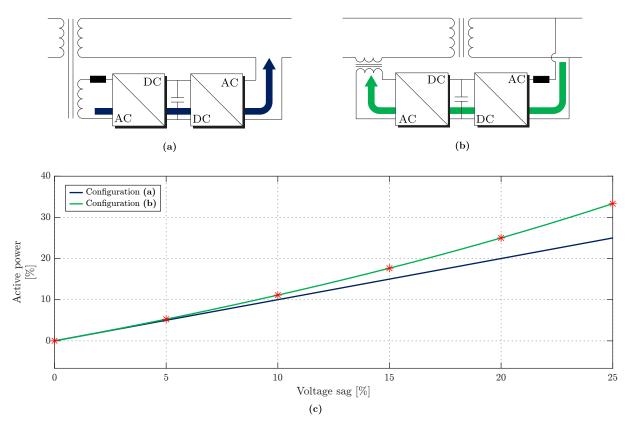

| 4.1  | HDT configurations and required active power                                       | 71       |

|------|------------------------------------------------------------------------------------|----------|

| 4.2  | HDT model to for CAPF analysis                                                     |          |

| 4.3  | Ideal steady-state CAPF behavior                                                   |          |

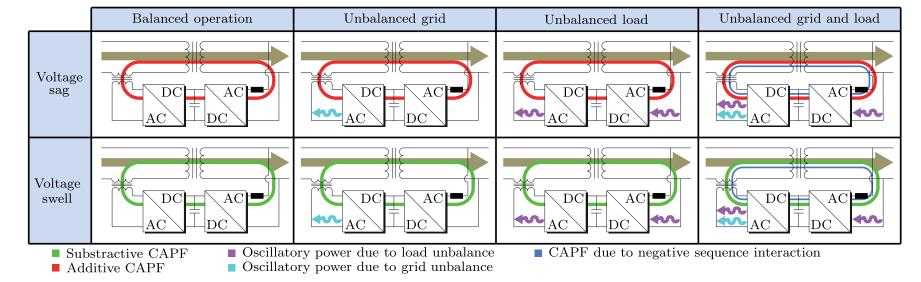

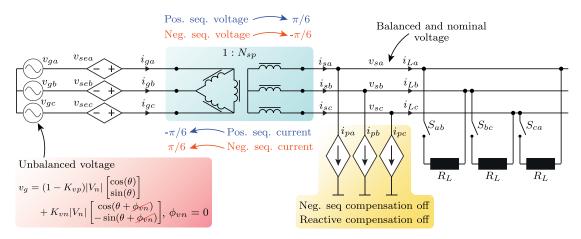

| 4.4  | CAPF and oscillatory power diagrams                                                |          |

| 4.5  | CAPF example under unbalanced load                                                 |          |

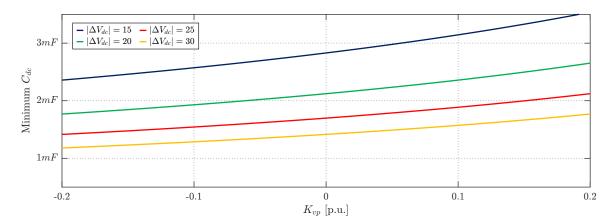

| 4.6  | Minimum DC-Link capacitance requirements                                           |          |

| 4.7  | Reactive power compensation - Reference circuit                                    |          |

| 4.8  | Reactive power injection mode - Operating vectors                                  |          |

| 4.9  | Reactive power injection - Operating region                                        |          |

| 4.10 | Power flow of an HDT connected to a BESS                                           |          |

|      | HDT controller for CAPF analysis                                                   |          |

|      | Load current filter for CAPF analysis                                              |          |

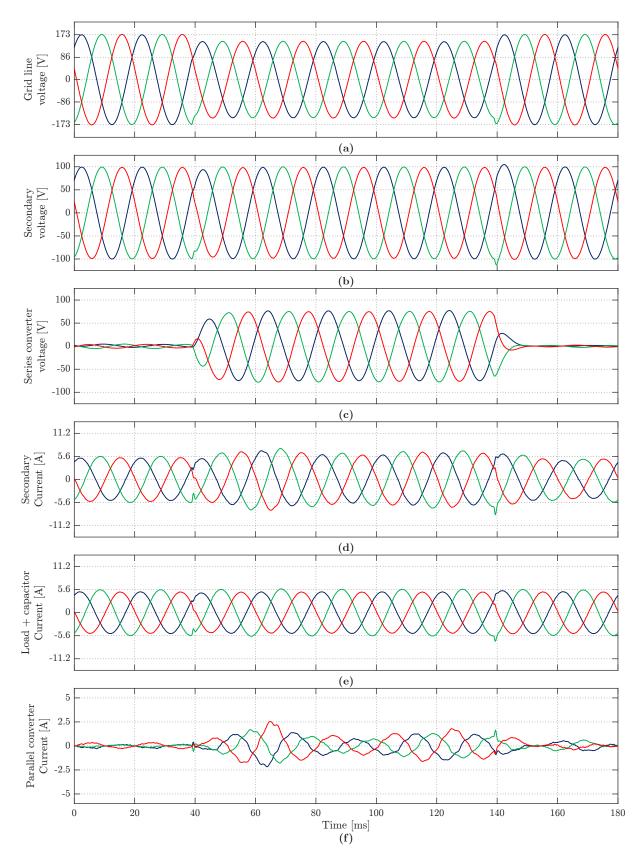

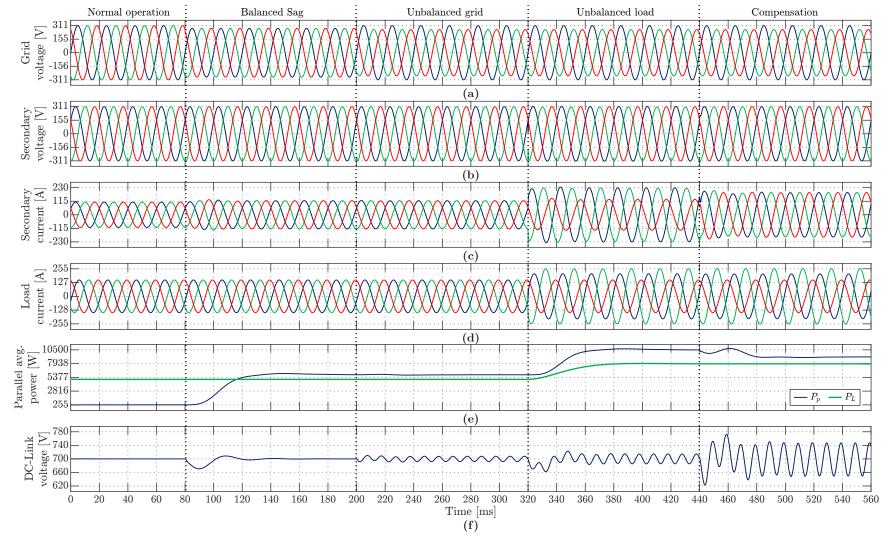

|      | Simulation results - Dynamic response of the HDT                                   |          |

|      | Experimental versus theoretical CAPF and efficiency                                |          |

|      | Experimental results - HDT response under varying conditions                       |          |

|      | Experimental results - CAPF with unbalanced load - Microcontroller                 |          |

|      | Experimental results - Reactive power injection                                    |          |

|      | Experimental results - HDT with BESS                                               |          |

|      |                                                                                    |          |

| 5.1  | General scheme of the HDT controller                                               |          |

| 5.2  | Control algorithm timing diagram                                                   |          |

| 5.3  | Series capacitor voltage controller                                                |          |

| 5.4  | Series capacitor voltage estimator                                                 |          |

| 5.5  | Grid voltage estimator                                                             |          |

| 5.6  | Parallel converter controller                                                      |          |

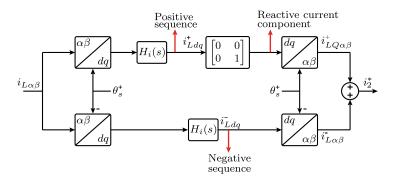

| 5.7  | Load current controller                                                            |          |

| 5.8  | Load current sequence decomposition                                                |          |

| 5.9  | Stability analysis - Root locus                                                    |          |

| 5.10 | Simulation results under varying conditions                                        |          |

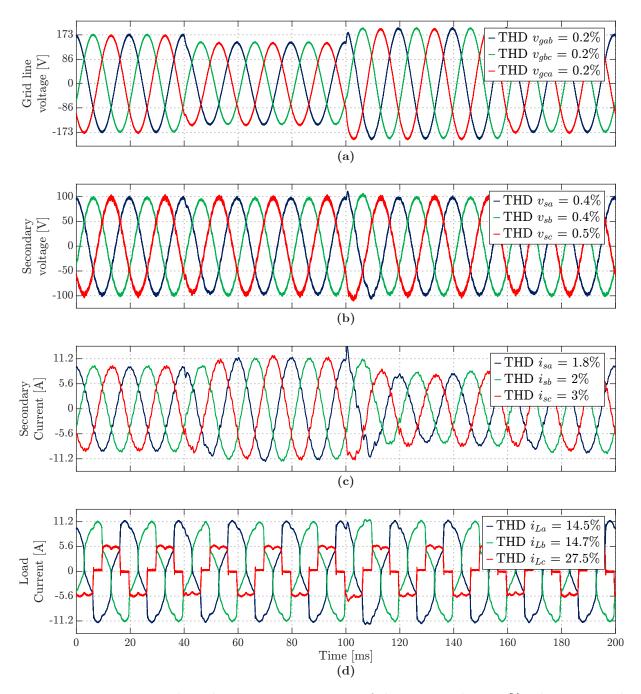

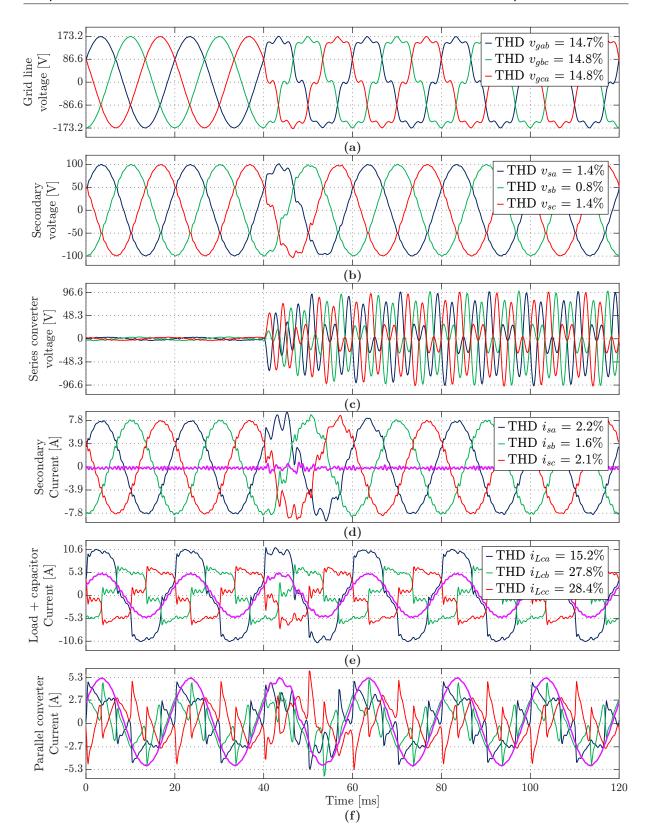

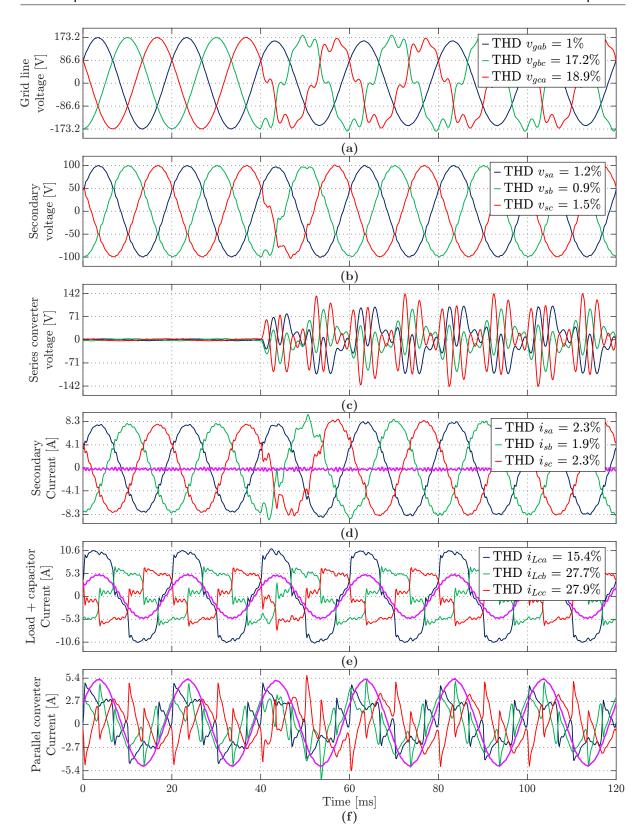

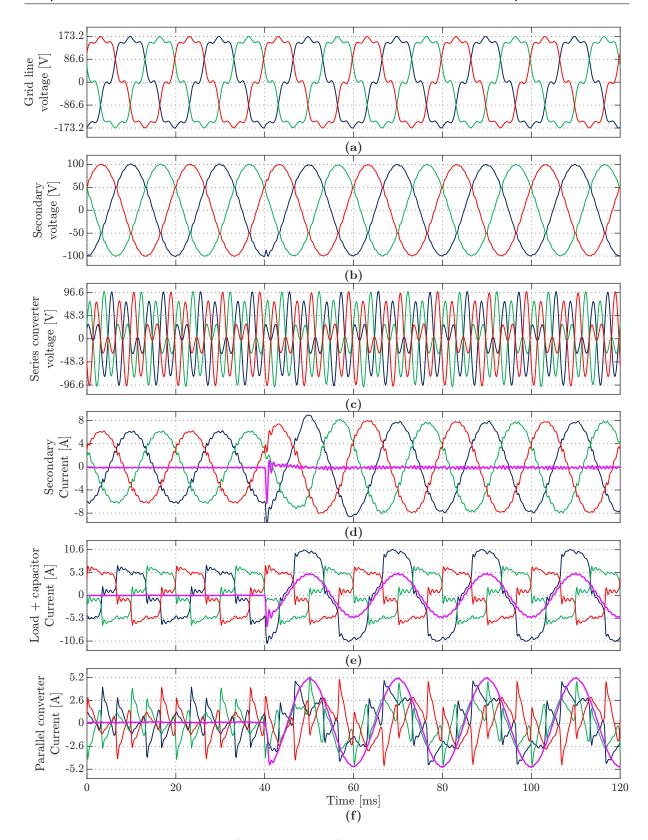

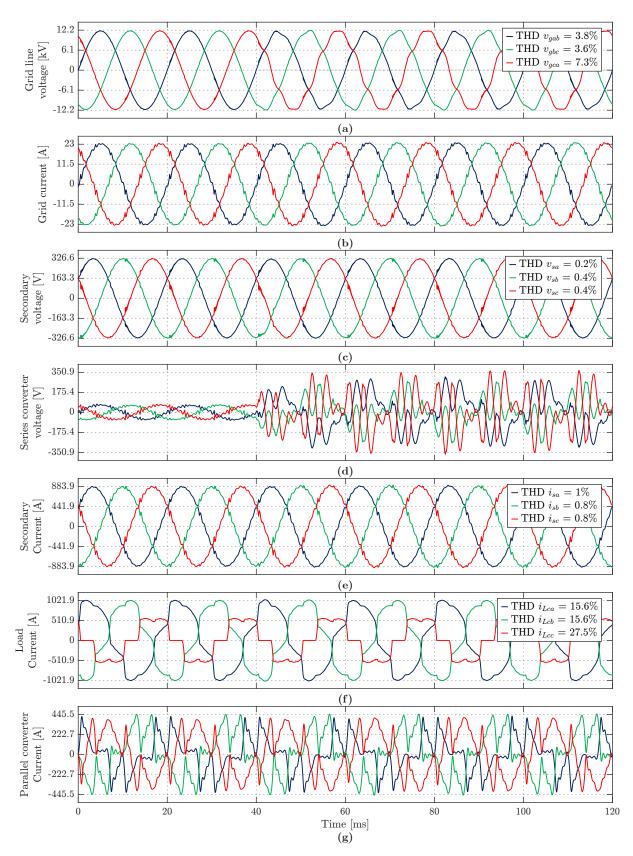

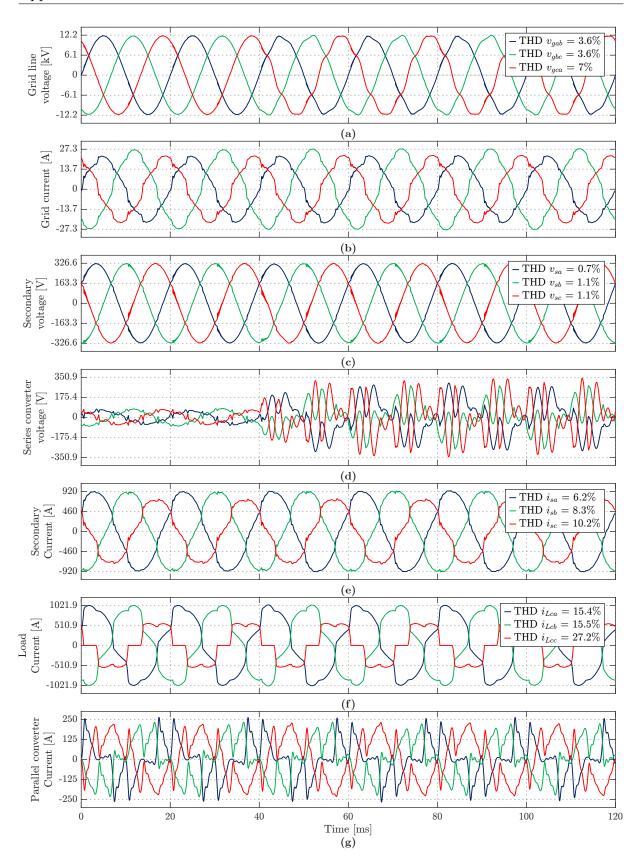

|      | Experimental results under voltage sag/swell                                       |          |

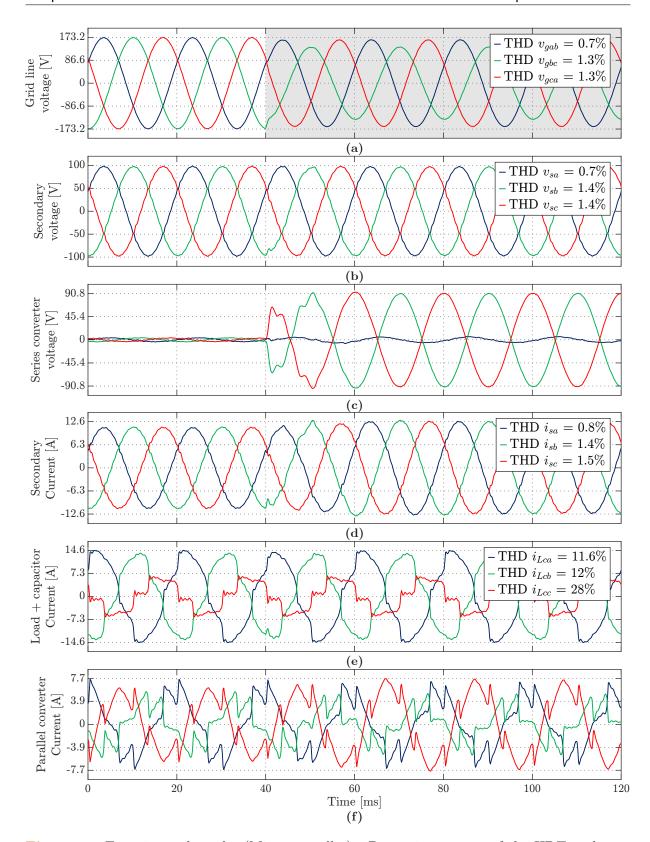

|      | Experimental results under an unbalanced grid voltage - Microcontroller $$ .       |          |

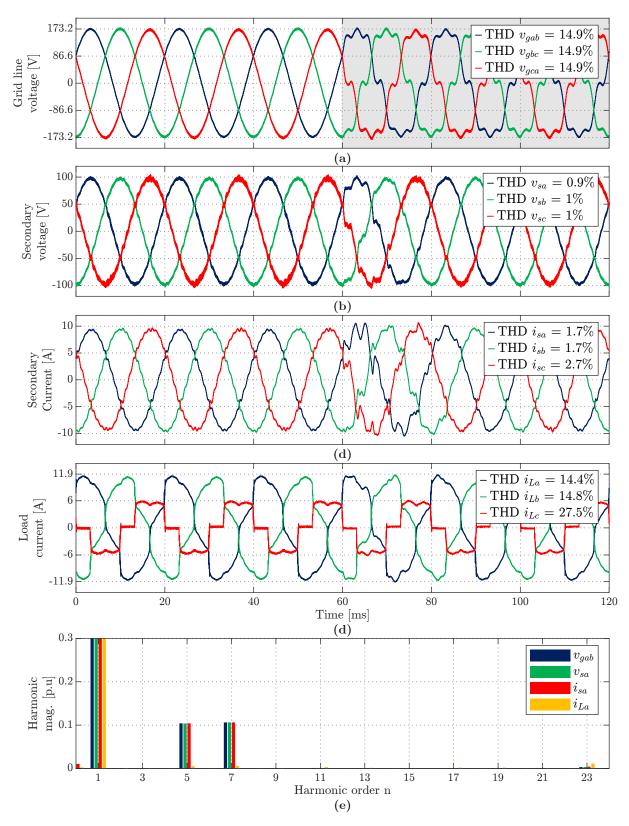

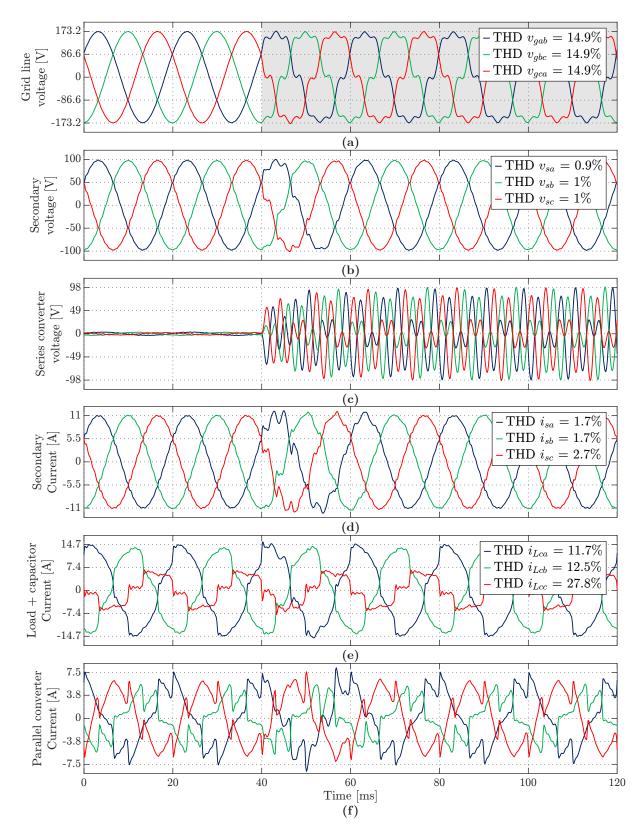

|      | Experimental results under distorted grid                                          |          |

|      | Experimental results under distorted grid - Microcontroller                        |          |

|      | Experimental results under distorted and unbalanced grid                           |          |

|      | Experimental results under distorted and unbalanced grid - Microcontroller         |          |

|      | Experimental results under a load step - Microcontroller                           | 154      |

| 5.18 | 4-wire grid - Experimental results under an unbalanced grid voltage -              |          |

|      | Microcontroller                                                                    |          |

|      | $4\mbox{-wire}$ grid - Experimental results under distorted grid - Microcontroller | 157      |

| 5.20 | 4-wire grid - Experimental results under distorted and unbalanced grid -           |          |

|      | Microcontroller                                                                    |          |

| 5.21 | 4-wire grid - Experimental results under a load step - Microcontroller             | 159      |

| 6.1  | HDT configuration                                                                  | 160      |

| 6.2  | LFT - Magnetic circuit                                                             |          |

|      | Flux example - With/without saturation                                             |          |

|      | 1 1145 VACULITARY - VV 1011/ VV 1011/1011/1011 (3/6b)111/(bb)(2/1)                 | 1 1 11 1 |

#### List of Figures

| 6.4 | Flux saturation - Simulation example                                     |

|-----|--------------------------------------------------------------------------|

| 6.5 | HDT controller                                                           |

| 6.6 | Flux estimator - Bode diagram                                            |

| 6.7 | Simulation result - No load                                              |

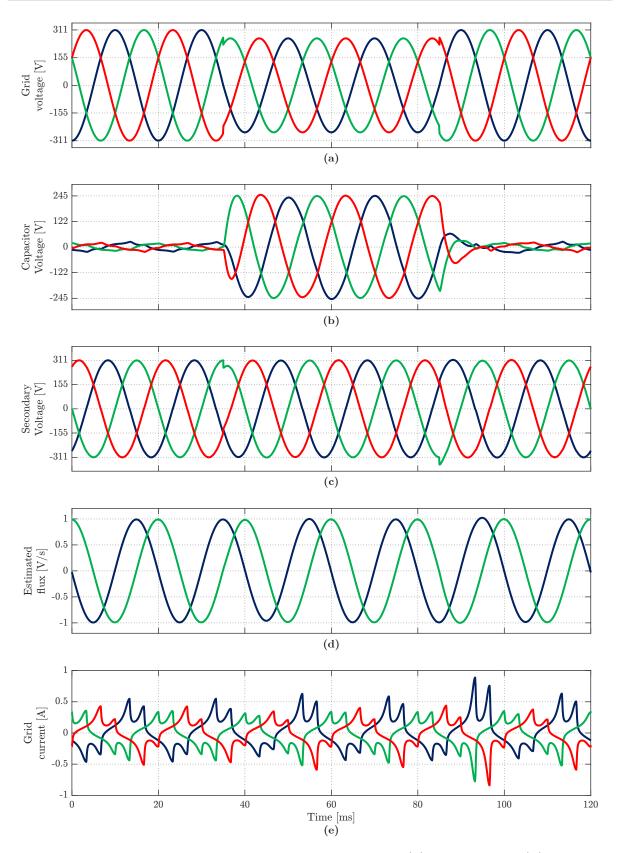

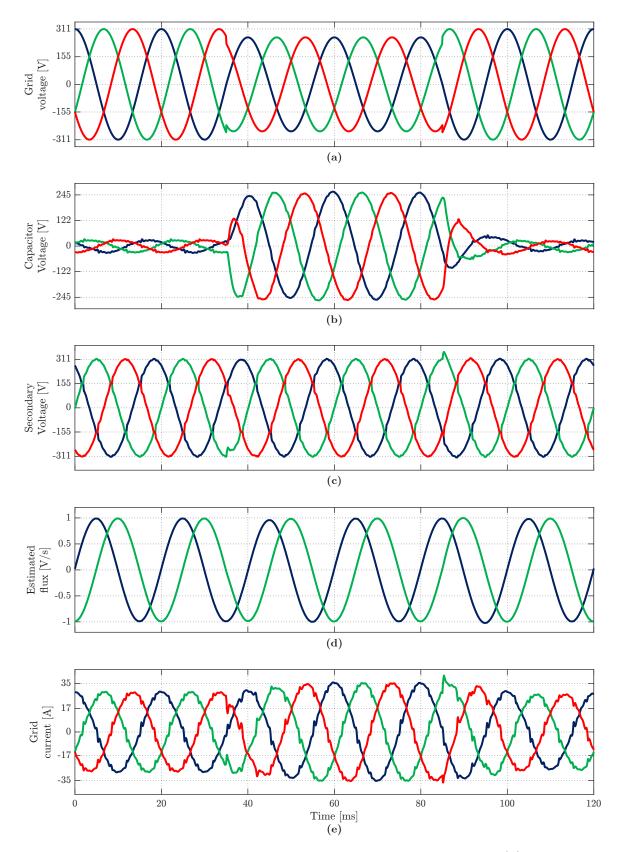

| 6.8 | Simulation result - Nonlinear load                                       |

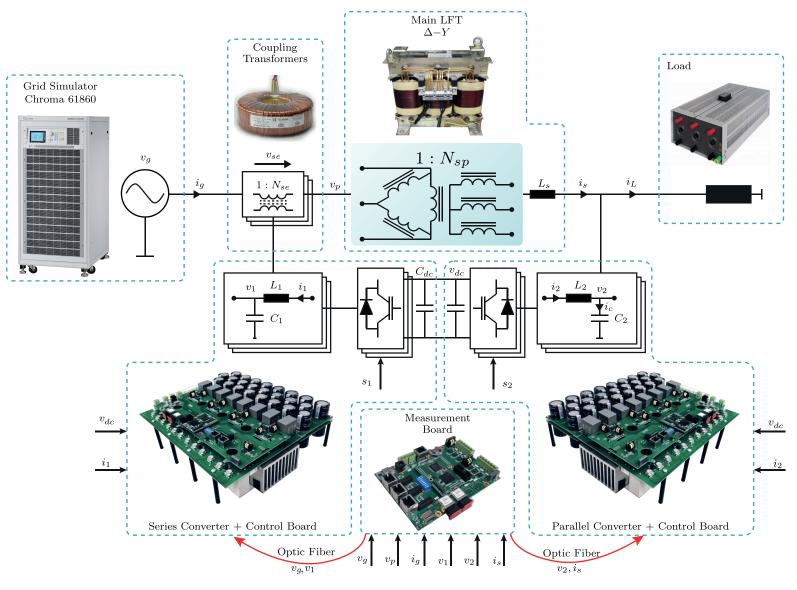

| B.1 | Setup diagram of <b>Chapter 3</b> - HDT under balanced conditions 184    |

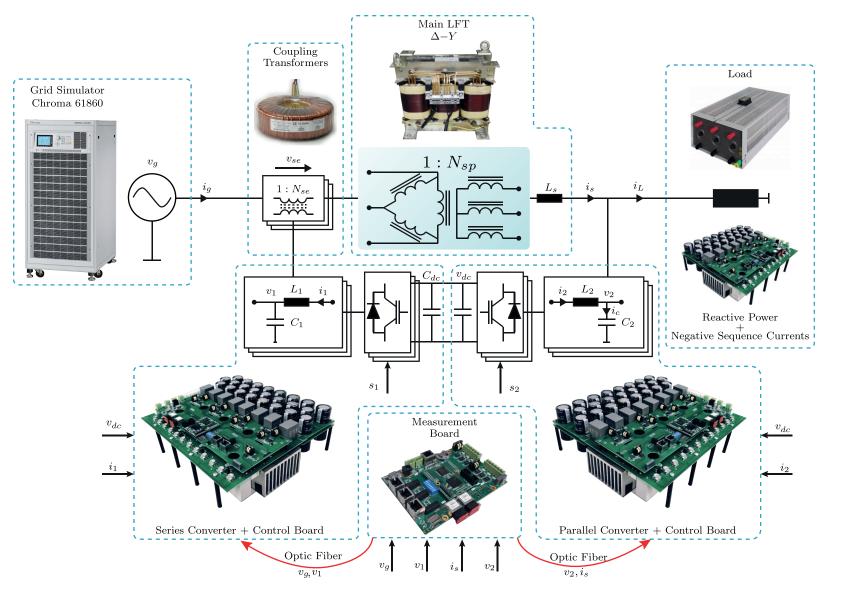

| B.2 | Setup diagram of <b>Chapter 4</b> - Efficiency experiment                |

| B.3 | Setup diagram of Chapter 4 - Unbalanced system and Reactive power        |

|     | injection                                                                |

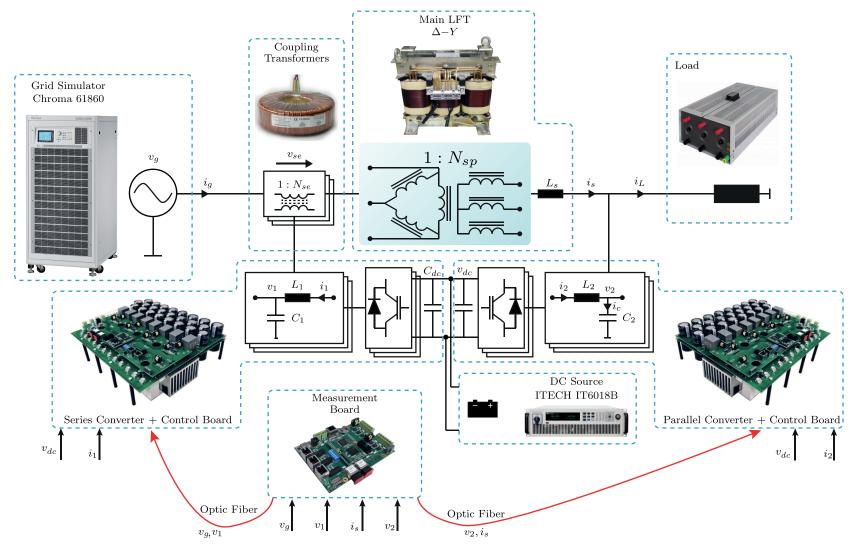

| B.4 | Setup diagram of Chapter 4 - HDT connected to a DC grid 187              |

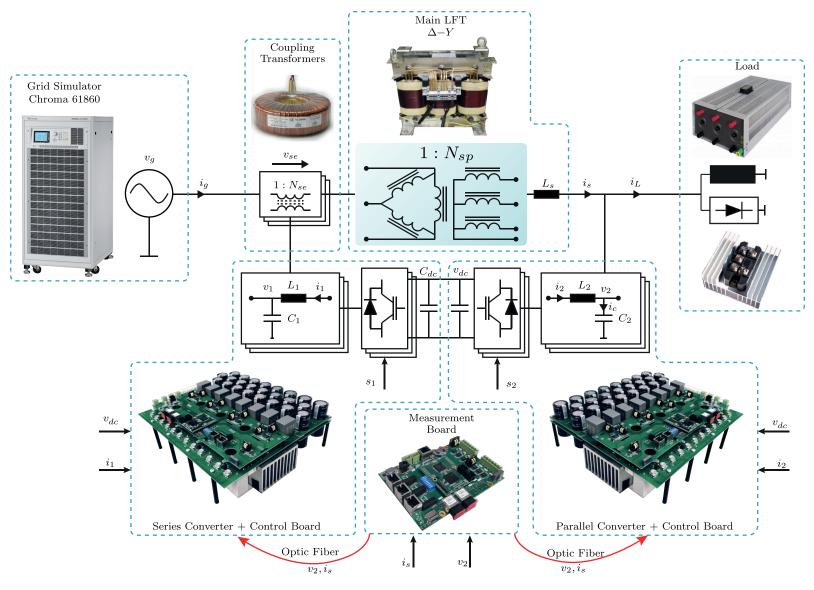

| B.5 | Setup diagram of <b>Chapter 5</b> - HDT connected to a polluted grid 188 |

| C.1 | Diagram MV/LV HDT                                                        |

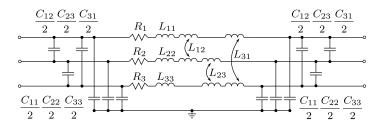

| C.2 | Distribution line - Distributed parameters model                         |

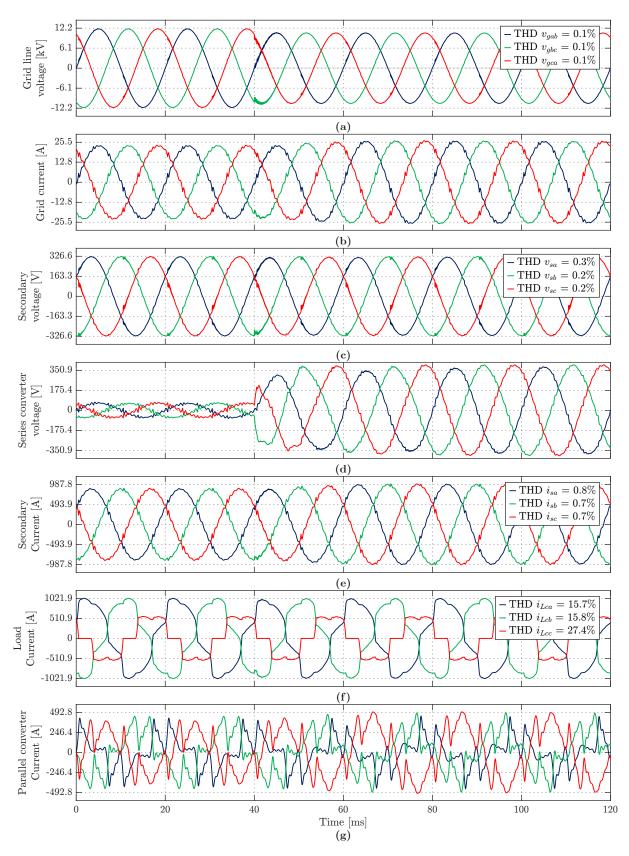

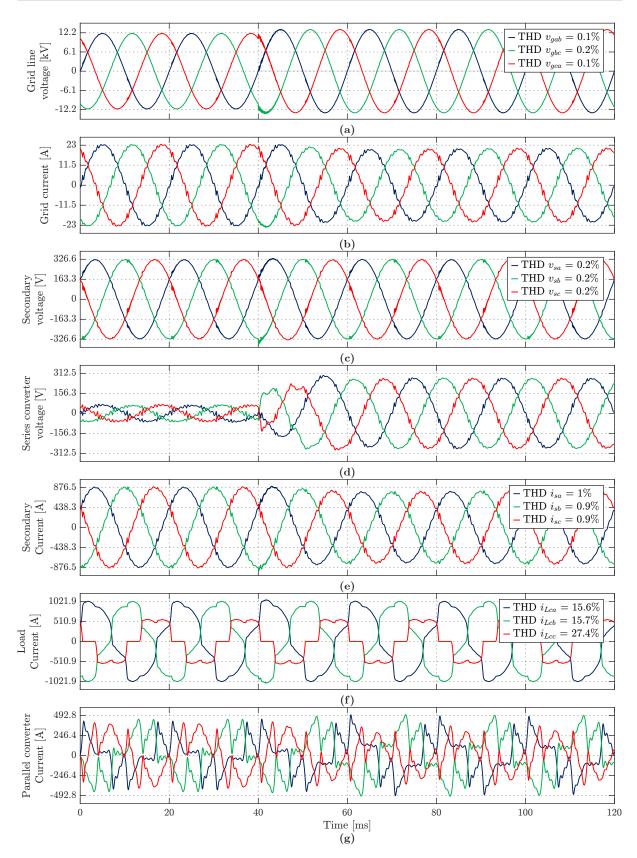

| C.3 | Simulation results under grid voltage sag                                |

| C.4 | Simulation results under grid voltage swell                              |

| C.5 | Simulation results under a distorted and unbalanced grid                 |

| C.6 | Simulation results with output current limiting                          |

# LIST OF TABLES

| HDT parameters for balanced conditions 61                     |

|---------------------------------------------------------------|

| Series converter - control parameters                         |

| Parallel converter - control parameters                       |

| HDT and control parameters for CAPF analysis                  |

| Grid voltage characteristic for negative sequence interaction |

| Simulation / Experimental parameters                          |

| Series converter - State feedback parameters                  |

| Series converter - Resonant terms                             |

| Series converter - Capacitor voltage observer                 |

| Series converter - Grid voltage observer                      |

| Parallel converter - State feedback parameters                |

| Parallel converter - Resonant terms                           |

| Parallel converter - Load harmonic estimator                  |

| Parallel converter - Load harmonic estimator                  |

| Parallel converter - DC-Link controller                       |

| Simulation cases - THD values                                 |

| Values for the unbalanced and distorted grid voltage          |

| Distribution line parameters                                  |

|                                                               |

# **ACRONYMS**

ADN Active Distribution Network

AW Auxiliary Winding

BESS Battery Energy Storage System

CAPF Circulating Active Power Flow

CT Coupling Transformer

DC Direct Current

FPGA Field Programmable Gate Array

GNC Generalized Nyquist Criterion

HDT Hybrid Distribution Transformer

HFT High-Frequency Transformer

LFT Low-Frequency Transformer

LQR Linear Quadratic Regulator

MIHDT Magnetic Integrated Hybrid Distribution Transformer

OPF Oscillatory Power Flow

PF Power Factor

PQ Power Quality

PV Photovoltaic

PWM Pulse Width Modulation STATCOM Static Compensator SST Solid-State Transformer THD Total Harmonic Distortion

UPQC Unified Power Quality Compensator

ZOH Zero Order Hold

# Chapter 1

# INTRODUCTION

**Remark:** This chapter is partly based on the following publication of the author:

[1] A. Carreno, M. A. Perez, C. R. Baier, A. Huang, S. Rajendran, M. Malinowski, "Configurations, Power Topologies and Applications of Hybrid Distribution Transformers", *Energies*, 2021.

Nowadays, there is an increasing interest and high research efforts in achieving a low-carbon and sustainable society, for which the penetration of clean energies such as Photovoltaic (PV) systems, integration of Battery Energy Storage Systems (BESSs), and efficient energy conversion are demanded. In this scenario, systems capable of processing bidirectional power flows, and providing precise voltage and current quality profiles are required. Therefore, the exclusive use of conventional Low-Frequency Transformers (LFT) as an interface between the Low Voltage (LV) grid and Medium Voltage (MV) grid is not sufficient to cope with the demands of the new power systems.

#### 1.1 The conventional and modern distribution grid

Distribution transformers are one of the pillars of the actual distribution grid. They are the interface between the MV and LV grid, stepping down the voltages to a safe and usable range for the end-users. They are characterized by being a highly robust and low-cost solution, being available in different winding configurations and power ratings according to the grid requirement and mounting type [1]. Transformers have an average lifetime above 35 years operating under rated conditions [2].

Power quality (PQ) is a term employed when referring to the power system voltage and current waveform quality at different points of the grid [3]. Low PQ phenomenons can be generated by the users, for example when consuming nonsinusoidal and unbalanced currents. Weak grids can be a source of PQ as well, providing unbalanced and variable frequency voltages. IEEE Std 1159-2019 and IEEE Std 519-2014 give guides on PQ measurements and recommended practices to comply with and guarantee a good quality service [4,5]. Some effects of low PQ are high voltage peaks that can damage equipment, heating, losses, acoustic noise, and lifetime reduction in equipment. For utilities, low PQ is translated into additional losses on transmission lines and generators or the failure of power systems elements that can jeopardize the correct grid operation [6]. The abnormal grid operation can cause considerable economic losses to the operator and end-user. Therefore, PQ problems must not be neglected [7].

Low PQ is more pronounced in distribution systems, due to the high number of variable, nonlinear and unpredictable loads connected to them. As low-voltage distribution grids are supplied by distribution transformers, these can be highly affected by the low PQ presented in these systems. When operating under these conditions, the transformer suffers higher core losses, which increase its hotspot temperature. This is a critical variable, as it is related to the winding isolation degradation and, therefore, decreasing the transformer lifetime [8].

Distribution transformers can be subject to different PQ problems in distribution grids when supplying nonlinear currents and nonlinear voltages [9, 10]. Industrial applications, such as elevators, rolling mills, arc furnaces, among others, consume high amounts of current in short periods, worsening distribution grid operation. PQ issues, such as flickering, can be generated due to the operation of industrial machinery [11]. Additionally, new kinds of loads establish new operating conditions for distribution transformers and the grid, for which they were not designed. For example, high penetration of wind and PV systems connected to the grid through power converters adds a degree of uncertainty to the grid operation due to the high variability of these

resources and also due to the harmonics injected by the power converters [12]. The distributed characteristic of these systems makes it possible that the voltage profile on the distribution grid can increase close to the connection points under high penetration periods [13]. This scenario can represent a problem for grid control systems, such as transformer tap changers, making them switch when it is not required [14]. On the other side, the widespread of electric vehicles can overload the grid. Charging algorithms for electric vehicles tend to delay the vehicle charging process to the night, due to economic incentives [15]. This scenario can overload the distribution transformers, reducing their lifetimes [16]. Several methods are proposed to reduce the impact on distribution transformers—for example, utilizing the power converter of distributed renewable energy resources for volt-var control, smart control system, intelligent and coordinated charging algorithms and including the distribution transformer hotspot model into the power converter control systems, the use of BESS in order to operate in periods of high energy demand, among others [16–18].

The regulating capabilities provided by a distribution transformer are limited. To deal with slow dynamic voltage variations, they are provided with on-load taps commutating systems, which allow for modifying the winding ratio without disconnecting the load. Nonetheless, these systems operate in a discrete manner and with dynamics in the order of seconds. Additionally, they are the main transformer failure cause, which jeopardizes the distribution grid, adding additional maintenance costs [19]. The use of electronic-assisted taps commutating systems is available, allowing for a decrease of the commutation times and losses. Nevertheless, they suffer additional conduction losses and operate in discrete voltage steps as well [20]. Distribution transformers do not have mechanisms to mitigate load current harmonics, being necessary to design them to operate under these conditions. These transformers are known as k-rated transformers [21].

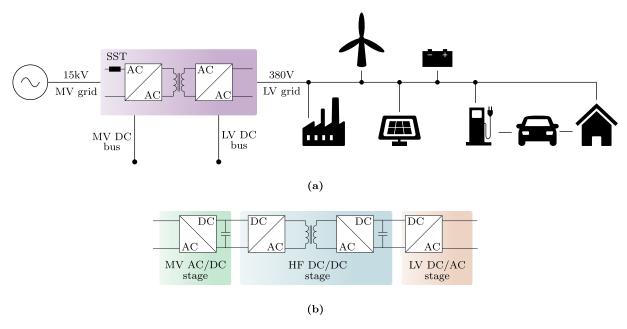

Solid-State Transformers (SSTs), shown in Fig. 1.1(a), are an attractive solution to cope with PQ problems. In this scenario, the conventional distribution transformer is fully replaced by a power electronics converter. Normally, SSTs consist of several conversion stages, which can be seen in Fig. 1.1(b). They are based on power electronics combined with High-Frequency Transformers (HFTs), allowing for fast and precise voltage and current control [22]. Some characteristics and advantages of SSTs are given below [23].

- High-quality voltage supply: Grid voltage disturbances, such as voltage unbalances and harmonics can be isolated, providing a sinusoidal voltage to the low-voltage side.

- High-quality grid currents: For example, SSTs can provide current harmonic mitigation, Power Factor (PF) correction and load balancing, and therefore improve

Fig. 1.1. Solid-State Transformer concept. (a). Generalized SST in a MV to LV distribution grid. (b) Typical conversion stages of an SST.

the current quality of the MV grid.

- DC port availability: Due to the conversion stages and depending on the SST topology, MV and LV DC buses are available.

- SSTs allow the integration of renewable energy systems and energy storage.

- Modularity and scalability

- Smart load management and advanced monitoring

Nonetheless, the efficiency of these systems is lower compared to other existing solutions, due to the necessity of operating with a high number of submodules and power conversion stages, and the processing of the complete power flow. Compared to a distribution transformer, the complexity of an SST, the additional power electronics, and the cost prevent the SST from being applied in the actual power systems [24]. However, the main reason relies on the reliability issues suffered by the SST. Distribution grids can be subject to different kinds of faults, in which short circuits can be highlighted. These high-amplitude currents can not be supplied by the STT without considering countermeasures, such as overrated design, incorporating rotating machines, and internal reconfiguration [25]. Therefore, hybrid solutions that lie between the conventional distribution transformer and the SSTs can be a promising solution.

#### 1.2 The Hybrid Distribution Transformer (HDT)

The concept of Hybrid distribution transformers (HDTs) is shown in Fig. 1.2(a), and they combine a distribution transformer with one or more power electronics conversion stages, which are designed to operate at a fraction of the nominal power of the distribution transformer. HDTs have attracted the attention of the industry, where ABB has filed several patents relating to their control, configurations and applications [26–29].

Nowadays, the available configurations, topologies, and control objectives are diverse. As can be seen, the HDT is the interface between the MV and LV grid, where the HDT is any nonspecific combination of power electronics modules connected with the distribution transformer [30]. Compared to the SST, the power converter stage corresponds to a partial power converter, and therefore the control capabilities are limited to the power converter rating. Typically the power converters are designed to operate at between 10% and 20% of the transformer nominal power [31]. Additionally, for the same reason, the efficiency of the power converter stages has a low impact on the overall conversion efficiency. The use of protection systems, such as bypass switches, varistors, and DC-Link clamping circuits, increases the power converter losses and volume. Nonetheless, due to the partial power converter, the protection systems have an insignificant impact on the overall efficiency and volume [32, 33]. There is no restriction on the power converter location, with works reporting several different connection possibilities, i.e., MV and LV side connections, each with its own advantages and disadvantages. Therefore, the HDT configuration and power converter location will determine the power converter topology, semiconductors rating, and the compensation that the HTD can provide [34].

Fig. 1.2(b) shows a highly researched HDT, in which the power converters are connected to an Auxiliary Winding (AW), and also in series with the LV grid [32]. This HDT employs an LFT with open winding, as shown in Fig. 1.2(c).

One of the main concerns with the applicability of new technologies in the grid is power system reliability. LFT can operate for several seconds under grid failures, such as short circuits. In contrast, power converters have a very limited short-circuit current supply capacity. In this regard, some HDT configurations can operate under faults, as the HDT configuration allows for the power converter to be disconnected during the fault, letting the LFT supply the short circuit currents, preserving the grid reliability [32].

Each HDT configuration and topology must be considered in the design of the HDT to provide a reliable operation; nonetheless, not enough research has been carried out in this area. In general, for HDTs with series-connected converters, it is considered a bypass switch that short circuits the power converter in the case of faults [31,35]. For

Fig. 1.2. Hybrid Distribution Transformer. (a) Concept. (b) Example HDT [32]. (c) Open winding configuration.

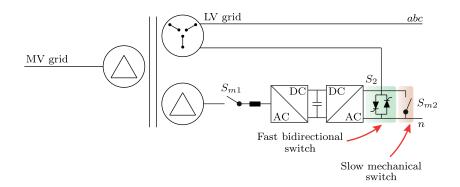

the configuration of Fig. 1.3, a comprehensive protection system design has been realized [32,33]. In the case of short circuits on the low-voltage grid, high currents are delivered by the transformer and the power converter. Therefore, in this situation, the power converter must be bypassed rapidly, allowing the transformer to deliver the short circuit currents. A bidirectional switch composed of antiparallel high current thyristors,  $S_2$ , is utilized, which provides a low-impedance path in less than  $100\mu s$ . Then, after the system is correctly bypassed, an additional mechanical switch,  $S_{m2}$  is activated to reduce the losses. At the same time, the mechanical switch for the parallel converter,  $S_{w1}$ , is utilized to connect the parallel converter during startup and disconnect it during failures. Additionally, the

Fig. 1.3. Hybrid transformer with bypass switch.

reliable design of the HDT considers diverse scenarios, such as lightning surges and MV surges, for which it is necessary to find a compromise between the AW ratio, power converter losses, semiconductor breakdown voltage, and filter size, among others.

A reliable HDT must be able to detect a dangerous operating condition and depending on the configuration, bypass and/or disconnect the power converter from the grid and transformer [35]. When done correctly, the HDT behaves as a conventional LFT, ensuring high reliability. Alternatively, reliability can be assessed according to the power converter topology and its under-fault operation capability. For example, for two-level converters, redundant legs can be included which can be switched on in the case of faults. Additional fault isolation circuits are mandatory to isolate the damaged leg as fast as possible [36]. On the other hand, for configurations connected to the MV side, the use of MV multilevel converters adds a level of reliability compared to, for example, two-level topologies. When a submodule of a cascaded multilevel converter fails, the system can be reconfigured to continue with its normal operation, without requiring to disconnect the power converter [37]. Nonetheless, the complexity and cost of the implementation scale up.

#### 1.3 HDT configurations

In this work, the HDT configurations are classified according to the energy source of the power converter unit, as follows:

- Floating capacitor.

- MV or LV side winding of the main LFT.

- AW of the LFT.

Simultaneously, each one can be classified according to the method utilized by the power converter to inject its energy into the grid, which is directly related to the kind of compensation it can provide. The injection methods can be classified as:

- Series injection.

- Series injection through Coupling Transformers (CTs).

- Parallel injection.

- Magnetic compensation.

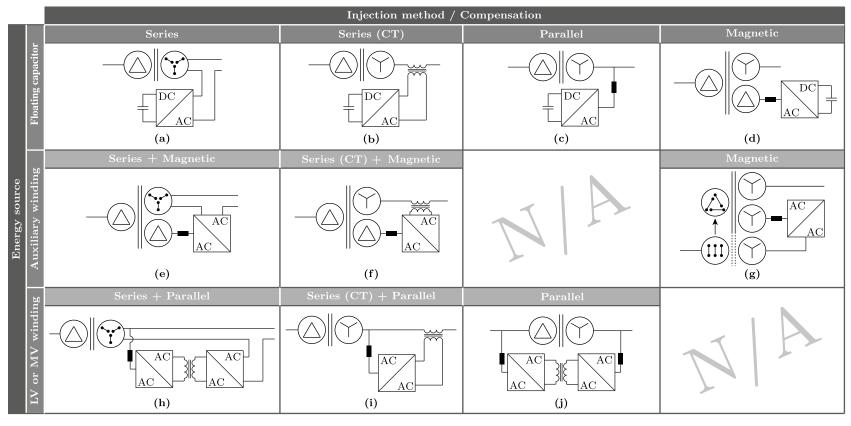

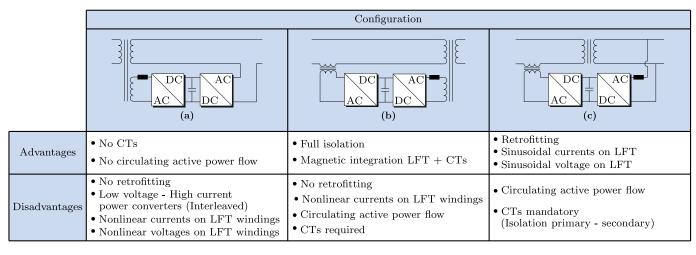

The HDT configurations, classified with respect to the energy source of the power converter and the injection method are summarized in Fig. 1.4.

In this section, HDT configurations are categorized regardless of the phase numbers of the grid, assuming that the power converter is fully controllable. Additionally, it is only in self-supported HDTs that the conversion method is shown, whereas in the remaining configurations, the power converters are generalized as AC/AC power converters. Although the operation region and injection capability are strictly tightened to the power converter topology, it is assumed that the power converters operate in a decoupled manner, and both terminals operate in the four-quadrant region [38].

#### 1.3.1 Self-supported HDTs

Self-supported HDTs, or HDTs where the energy is obtained from DC capacitors, are presented in Fig. 1.4(a)–(d). Regardless of the power converter connection method, the power converter can only provide reactive power compensation when utilizing DC capacitors as the energy source. An additional control method based on active power is required to charge and regulate the capacitor voltage to its rated value. Active power compensation can be provided when integrating DC sources into the DC-Link.

The configuration of Fig. 1.4(a) is utilized to provide voltage regulation to the distribution grid [30]. No isolation is required when the power converter is connected between the neutral point and the LFT winding. Moreover, if the neutral point is inaccessible, connecting the power converter to the distribution line without CTs is possible by utilizing single-phase power converter topologies [39]. Alternatively, the integration to the distribution grid can be realized utilizing CTs, as configuration Fig. 1.4(b) shows, allowing for the use of three-phase power converter topologies instead of single-phase configurations, reducing the converter elements. Integrating a DC source into the DC-Link, such as a battery bank, allows voltage control utilizing active power,

Fig. 1.4. One-line representation of the HDT configurations. (a) Power converter connected in series without a coupling transformer (CT). (b) Power converter connected in series with CT. (c) Power converter connected in a parallel configuration. (d) Power converter coupled to the core of the LFT. (e) Power converter connected to AWs and in series without CT. (f) Power converter connected to AWs and in series with CT. (g) Power converter connected to two AWs. (h) Power converter connected to the LV side and in series without CT. (i) Power converter connected to the LV side and LV sides of the LFT in a parallel configuration.

extending the converter regulation capabilities [40]. Additionally, thanks to the CTs, the power converter can be connected to the MV grid [41].

The configuration of Fig. 1.4(c) provides shunt compensation by connecting the power converter to the LV side [30]. This configuration can be integrated into the LV distribution grid with or without CTs [42]. It is possible to utilize the same configuration connected to the MV side. Nonetheless, unless multilevel power converter topologies are employed, CTs are required to connect the converter output due to the higher voltage levels [43]. Alternatively, MV semiconductors have been researched to achieve a direct connection to the MV grid [44, 45]. Another alternative to cope with the connection to MV is to utilize the LFT taps to reduce the AC voltage connection level and the minimum required DC-Link voltage. This solution has been proposed as a Static Synchronous Compensator (STATCOM) integrated into the LFT with and without passive filter branches [46]. Nonetheless, the current distribution of the MV winding is not equal, causing overcurrents and damaging the windings. Therefore, the reactive power compensation must be limited according to the load PF in order to avoid failures [47]. The same idea has been proposed and applied to the LV side taps, to additionally provide active filtering [48].

It is possible to connect the power converter to an AW of the LFT to provide magnetic compensation, as Fig. 1.4(d) shows. In this case, the LV winding and AW share the same core path and, therefore, the same magnetic flux, equivalent to a power converter connected in an electrical parallel configuration [30]. One application of this configuration provides current filtering in large-power industrial rectifiers and shipboard power systems [49,50]. The AW can contain tuned filter branches, which can be actively controlled to mitigate characteristics harmonics of nonlinear systems [51].

#### 1.3.2 HDTs connected to auxiliary windings

The HDT configurations presented in Fig. 1.4(e)–(g) correspond to those configurations in which the power converter obtains its energy from an AW of the LFT. The main characteristic of these configurations is that the AW provides magnetic isolation, allowing the synthesis of a single-phase voltage, which can be connected in series to the distribution line. Then, depending on the system phase numbers and power converter characteristics, one of the three configurations should be utilized, as explained below.

In the configuration of Fig. 1.4(e), the power converter can be connected in series to the secondary side of the transformer if:

- 1. The transformer has an open windings configuration

- 2. The neutral connection must be realized on the power converter side

Most of the research studies on HDTs have focused on this configuration, and different power converters have been applied to it. Additionally, several patents that utilize this configuration have been filed by ABB [26–29]. HDTs based on unidirectional power converters have been proposed. Nonetheless, their operation region highly depends on the grid and load conditions [52]. On the other hand, solutions based on back-to-back AC/DC power converters extend the regulation capabilities, providing voltage and current control in a broader range [53]. Additionally, it is possible to utilize AC/AC chopper converters. Nonetheless, the regulation capabilities depend on the utilized power converter topology and the grid impedance matching. Moreover, depending on the converter topology, under grid faults, and after bypassing the power converter, the LFT cannot provide rated voltage due to unconventional ratios of the secondary and AWs. These issues are solved by utilizing bipolar AC/AC power converters [35]. Another alternative is to utilize three-phase AW for each output phase in conjunction with DC-Link-based power converters. In this case, independent DC-Links per phase are required, simultaneously allowing for connecting the power converter in series to the distribution line without CTs after the LFT output terminals. The three-phase output voltages are magnetically isolated between them. Moreover, different winding configurations can be utilized to mitigate harmonic currents generated by the power converter switching process [54].

In the configuration of Fig. 1.4(f), the series converter is integrated into the distribution grid through CTs. In conjunction with the CT, the AW isolates the power converter from the grid, which allows for optimization and reduction of the DC-Link voltage independently of the series converter location. There are solutions based on back-to-back AC/DC converters [34], as well as based on AC chopper converters [55,56]. Connecting the series converter to the MV side can protect the LFT from grid voltage disturbances, providing the required mitigation on the MV grid [57]. A detailed model and compound control scheme has been presented for this configuration. The model accounts for the voltage and current disturbances, aiming to improve the robustness of the system [58]. Additionally, controllable tuned filter branches have been proposed for the shunt converter to mitigate characteristics harmonics. The power converter can actively regulate the filter impedance for harmonics mitigation purposes [59].

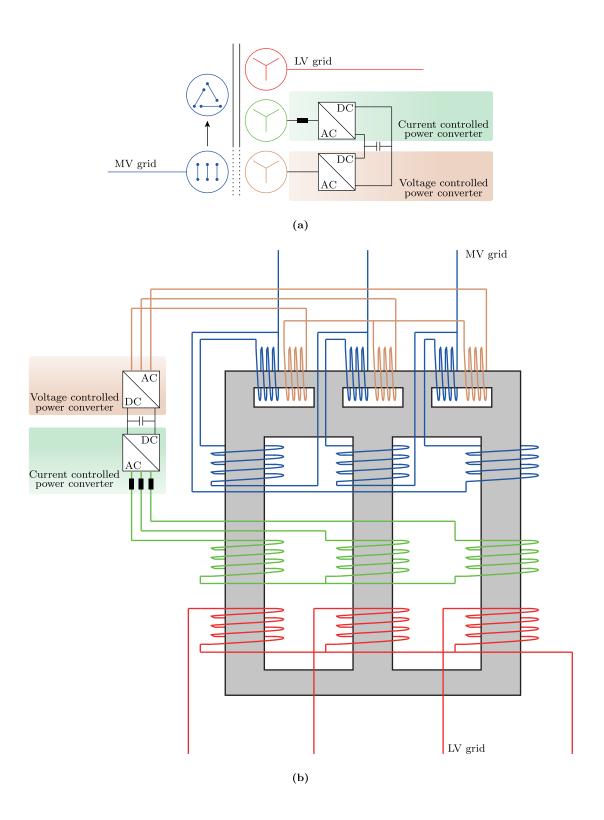

An alternative to the previous configurations is the Magnetic Integrated Hybrid Distribution Transformer (MIHDT), shown in Fig. 1.4(g). This configuration fully integrates the power converter into the main LFT. In this case, the power converter takes its energy from an AW, which, after being processed, is injected back into the LFT through an additional AW. The core and winding configuration determine the purpose of the power converter.

One specific configuration of MIHDT has been published as a Power Electronics

Integrated Transformer (PEIT) and Custom Power Active Transformer (CPAT). Two equivalent parallel electrical circuits can be realized using two windings sharing the same magnetic core path, whereas a series electrical circuit is made by a winding attached to a third core leg or a shunt magnetic core path [60]. A single-phase PEIT has been proposed, whereas the three-phase alternative is obtained by connecting three single-phase PEITs [61]. In order to increase the level of integration, a shell-type structure is utilized, sharing the transformer yokes, which finally reduces the transformer footprint [62]. This configuration can be utilized as a power flow controller while providing current and voltage harmonics mitigation [63]. Another MIHDT has been proposed, which is shown in detail in Fig. 1.5 [64]. In this HDT, the main LFT integrates the CTs into the main core, as well as the power converter filter inductors. The latter are not shown in the diagram in order to simplify it. This alternative allows for a reduction of the amount of magnetic material and copper utilized.

#### 1.3.3 HDTs connected to transformer windings

Configurations of Fig. 1.4(h)–(j) show HDTs where the power converters obtain their energy from the MV or LV windings of the LFT. Since the power converter is directly connected to the windings of the LFT, an isolation stage is required to synthesize an isolated series voltage or to maintain the isolation between the MV and LV grid when it is required. As shown in the presented configurations, this task can be done through CTs or internal-isolated power converters.

In the configuration of Fig. 1.4(h), the power converter takes its energy from the LV winding, and after processing it, it is injected in series to the distribution line. The transformerless series connection is possible due to an internal isolation stage based on HFTs. This configuration has been proposed for a single-phase HDT, which, compared to solutions based on CTs and connected to AWs, allows for a reduction in weight and volume while being a retrofit and scalable solution [65–68]. On the other side, the configuration of Fig. 1.4(i) provides current and voltage compensation on the LV side. This configuration requires the use of CTs to allow the injection of a series voltage to the distribution line. This configuration is proposed based on back-to-back DC-Link-based power converters [53], and with three-phase direct AC/AC converters as well [69].

In Fig. 1.4(j), the power converter is connected to the MV and LV side in a parallel configuration utilizing power converters isolated by HFTs. For example, this configuration is utilized for the integration of renewable energy systems or when it is desired to increase the distribution transformer capacity without replacing it. In principle, this configuration does not allow proving series voltage regulation directly; nonetheless, it can be controlled

Fig. 1.5. Integrated Magnetics HDT. (a) Simplified diagram. (b) Winding diagram [64].

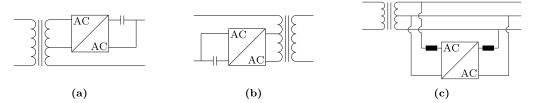

Fig. 1.6. Other HDT configurations. (a) Series connection to the high voltage taps. (b) Series connection to the low voltage taps. (c) Shunt connection to both phases of a single-phase grid with central tap.

indirectly through reactive power injection. A three-phase converter utilizing isolated DC/DC converters is proposed, as well as a single-phase isolated AC/AC converter [70,71].

### 1.3.4 Other HDT configurations

In this section, HDT configurations that are less common and do not fit within the previous classification are presented in Fig. 1.6.

In the configuration of Fig. 1.6(a), the power converter is connected to the high-side taps of the LV winding of the LFT. This configuration uses single-phase AC/AC converters per phase, and it was introduced as a controllable network transformer, which can provide power flow control between lines. The nature of the AC chopper converters preserves the input voltage phase without allowing for the modification of the output voltage phase. Nonetheless, utilizing techniques based on harmonics injections, it is possible to shift the fundamental voltage to provide power flow control and act as an active power filter [72,73]. Configuration of Fig. 1.6(b) applies the same idea. The power converter is connected to the neutral-side taps of the MV winding of the LFT. Compared to previous configurations, this solution presents lower conduction losses since the converter is located on the MV side. When utilizing AC chopper converters, switches must commutate between boost and buck mode for sag and swell mitigation, respectively [74]. Alternatively, DC-Link-based converters can be utilized. In this case, the taps-side converter rectifies the tap voltage, and then the end-side converter generates the required AC voltage, injecting it in series to the grid. No switches are required since DC-AC converters can shift their output voltage [75]. In this configuration, load harmonics mitigation is not provided, which can affect and diminish the LFT lifetime.

Finally, the configuration observed in Fig. 1.6(c) is proposed exclusively for LV distribution systems with central tap connection. The power converter is connected between both phases to provide parallel compensation. Additionally, it allows for active

and reactive power sharing between both phases for balancing purposes, reducing the neutral currents [74]. The parallel units can correct the PF and protect the LFT from load harmonics.

### 1.4 Power converter location effects

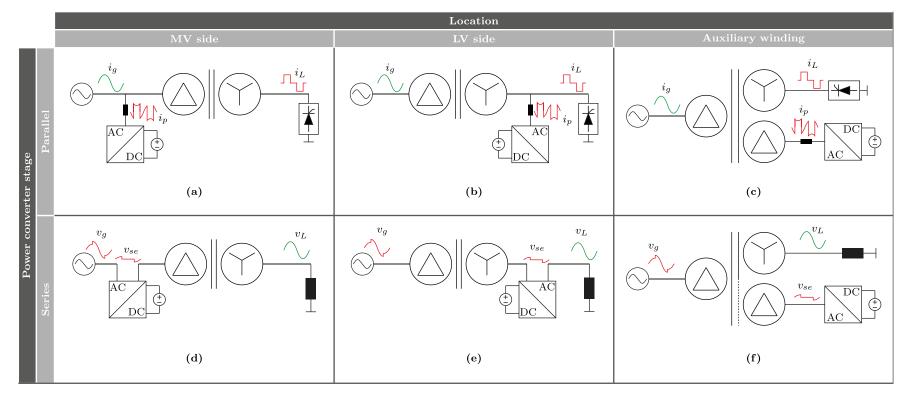

The location of the power converter has a decisive role in protecting the LFT, as it can prevent the load and grid voltage harmonics propagation. This is summarized in Fig. 1.7.

#### 1.4.1 Shunt converter location

The power converters connected in parallel configuration can be placed into the MV side, LV side, or AW, as shown in Fig. 1.7(a)–(c), respectively. The different power converter locations share the capability of improving the MV grid PQ by providing, for example, PF correction, harmonics filtering, and neutral current mitigation.

When the parallel converter is placed on the MV side, as seen in Fig. 1.7(a), and in the presence of nonlinear loads, these are not mitigated on the LV side and they are free to flow through the LFT. Distorted currents circulating on the LFT harm the lifetime of the LFT by generating additional losses, acoustic noise, and vibrations. The winding temperature, specifically its hot spot, is a critical variable for LFT as it impacts the winding isolation health. Therefore, the LFT lifetime decreases as no mitigation system is placed on the LV side. One method to deal with harmonic currents on the LFT is transformer derating. Alternatively, suppose the parallel converter is placed on the LV side, as shown in Fig. 1.7(b). In that case, load harmonics can be compensated, preventing their circulation on the LFT and improving the LFT lifetime. Additionally, the connection of the parallel converter on the LV side can be achieved with simple power converter topologies without requiring multilevel alternatives or CTs.

When the power converter is connected to an AW, as in Fig. 1.5, it can provide current regulation by means of the magnetomotive force compensation. Under this scenario, the negative effects of the load currents on the MV side current can be mitigated. Nonetheless, load harmonic currents still circulate through the LV side winding. Moreover, in order to compensate for those currents, the power converter must inject the required compensating harmonics currents into the AW, as represented in Fig. 1.7(c). The compensating currents depend on the load characteristic, the MV and LV winding ratios, and the AW configuration. Although the MV side winding currents are compensated in terms of PQ, the currents circulating through the LV and AW can contain high amounts of harmonics.

Fig. 1.7. Parallel and series converter locations. (a) Parallel converter connected to the MV side. (b) Parallel converter connected to the LV side. (c) Parallel converter connected to the AW. (d) Series converter connected to the MV. (e) Series converter connected to the LV side. (f) Series converter connected to the AW.

Therefore, the LFT must be designed to operate under these conditions.

#### 1.4.2 Series converter location

Power converters connected in series to the distribution line can mitigate voltage-based PQ problems, such as grid voltage sags, swells, voltage unbalances, and voltage harmonics.

As with the parallel converter, the location of the series converter has a significant impact on the LFT. When the series converter is placed on the MV side, as in Fig. 1.7(d), the supplied voltage to the LFT can be regulated, improving LFT performance and simultaneously controlling the load voltage. The same effect can be obtained if the converter is placed on the LV side, as in Fig. 1.7(e). Nonetheless, the LFT is unprotected from voltage disturbances, which can cause additional losses and inrush currents that can distort the rest of the grid.

An alternative to previous methods consists of connecting the power converter to an AW, as in Fig. 1.7(f) and Fig. 1.5. Depending on the specific magnetic configuration of the LFT, the harmonic voltages from the grid and those injected by the power converter might affect the magnetic core paths associated with their windings. The resultant magnetic flux circulating in the magnetic path associated with the LV side winding will be improved as well as the resultant voltage waveform on the output converter terminals. The magnetic core legs of the MV and AW will be under the stress of disturbed voltage, causing additional core losses. Especially considering nonlinear reluctance, voltage disturbances can cause inrush currents on both circuits.

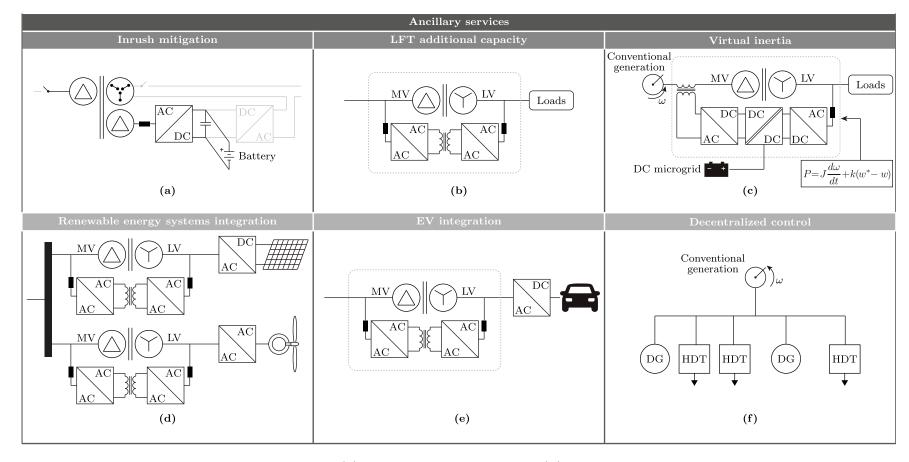

### 1.4.3 Combined compensation and circulating active power flow

It is possible to combine the series and shunt converters into one solution, as shown in the configurations of Fig. 1.4(e)–(i). Among these configurations, two groups can be highlighted. Configurations of Fig. 1.4(e)–(f) take their energy from the AW and inject them in series to the distribution line. On the other hand, configurations of Fig. 1.4(h)–(i) take their energy from the LV winding and inject them in series to the grid. In both groups, two scenarios can be studied according to the location of the series converter, i.e., if the series converter is connected to the MV or LV side.

Taking configuration Fig. 1.4(i) as a reference and connecting the series converter on the LV side, the power flow is shown in Fig. 1.8(a). It can be seen that part of the power flow deviates through the power converter stage in order to be processed and later injected in series to the grid.

A feedback phenomenon exists when the CT is connected on the MV side, as

Fig. 1.8. Active power flow scenarios. (a) No CAPF between the LFT and the power converter. (b) CAPF between the LFT and power converter. (c) Power converter and LFT active power.

in Fig. 1.8(b), increasing the power demand through the main LFT. The additional amount of power circulating between the main LFT and power converters is treated as a Circulating Active Power Flow (CAPF) in this work, and a detailed study of this phenomenon is presented in **Chapter 4**.

The CAPF between the LFT and the power converter exists in the presence of a voltage disturbance. In periods of high load, the additional power can overload the LFT, which could affect its lifetime.

Fig. 1.8(c) presents the required injected active power by the power converter in order to compensate for different grid voltage sags, as well as the total amount of active power processed by the LFT for both configurations. These values are calculated assuming the power converter and the LFT are ideal. As expected, the additional power requirements increase as the voltage sags to compensate are higher. If the power converter losses are considered, higher active power values will be required to compensate for voltage sags, decreasing the overall efficiency. Additionally, if the LFT losses and leakage impedances are considered, the additional CAPF required generates additional voltage drops, which the power converter must regulate. Therefore, the power converter must compensate for the grid voltage sag and the voltage drop generated by its operation, representing a higher

equivalent voltage sag, increasing the required CAPF and losses.

### 1.5 Applications of HDTs

In terms of cost, an HDT is expected to have a higher price than a conventional LFT due to the inclusion of the power converter. Some aspects that will determine the cost of an HDT are the number of power converters considered, i.e., the number of series and parallel converters and the power converter topology. The converter location plays an important role in the costs, as integrating the power converter into the MV is more technically challenging than its LV counterpart. The latter requires the use of multilevel power converters or MV protections and isolators. Beyond the cost of the power converter, the additional services that the HDT can provide make it an interesting alternative for electrical companies.

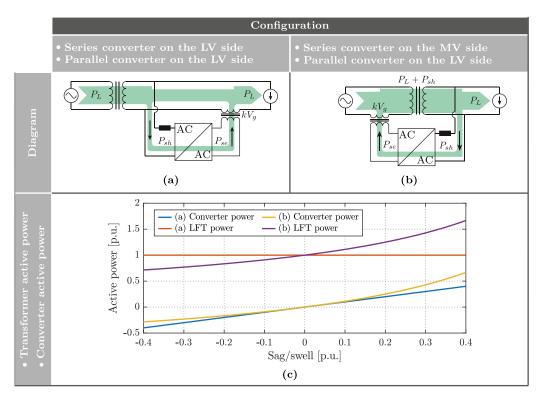

Besides the previously mentioned capabilities of an HDT, such as current and voltage harmonic filtering, PF correction, voltage regulation, load balancing, and neutral current mitigation, additional applications of HDTs have been researched, and are summarized in Fig. 1.9. The provided service and its impact on the grid or distribution transformer will depend on the selected HDT configuration and topology. Some of these services are presented in the following subsections.

### 1.5.1 Distribution transformer inrush current mitigation

There are several methods to reduce the impact of inrush currents at the moment of the distribution transformer connection, for example, by connecting the transformer phases in sequences at optimal moments. Nonetheless, it is possible to use the parallel stage of HDTs to mitigate their impact. Based on Fig. 1.9(a), and using a prefluxing technique, the power converter induces a magnetic flux equal to that induced by the grid at the connection instant, reducing the generation of inrush currents. Once the transformer is connected to the grid, the power converter can be synchronized to the LV side to initiate its normal operation, regulating the LV side voltages and currents. When it is desired to disconnect the transformer, the same technique is applied, but in the reverse order, until the transformer flux is zero. This feature is proposed utilizing the configuration of Fig. 1.4(e) along with a DC storage system connected to the DC-Link to provide the necessary energy to magnetize the transformer [76].

Alternatively, the same configuration can be applied to reduce magnetizing flux DC offsets, which generate inrush currents. The mitigation is carried out by the power

Fig. 1.9. Ancillary services provided by HDTs. (a) inrush current mitigation. (b) Increase in an LFT capacity by means of an HDT. (c) HDT to provide virtual inertia. (d) Renewable systems integration. (e) Electric vehicle charging station. (f) Voltage regulation of an ADN by means of HDTs.

converter module connected to the AW, modifying the core flux [77].

### 1.5.2 Distribution transformer additional capacity

By means of a parallel connection of a power converter isolated with HFTs, such as the configuration of Fig. 1.4(j), and by utilizing active and reactive power control, it is possible to increase the capacity of an LFT. This scenario is represented in Fig. 1.9(b). The power control is designed to supply a proportion of the load while providing PQ mitigation services. Proposed solutions integrate a full-rated power converter parallel to the conventional transformer [71,78,79].

### 1.5.3 HDTs to provide virtual inertia

In HDT with DC ports, it is possible to employ BESS or distributed generation systems to provide grid frequency support. This solution is attractive in low-mechanical inertia grids, where HDTs can be exploited [80]. Additionally, if multiple units are employed in a power system, their impact can be significantly improved. Fig. 1.9(c) shows the DC system integration to the DC-Link of the HDT to provide grid frequency support.

An external control loop can improve the grid inertia, which allows the softening of the frequency dynamic behavior under contingencies, providing primary frequency support. The control is based on modifying the converter injected power according to the grid frequency variation, emulating the synchronous generator mechanical equation [81,82].

# 1.5.4 Renewable energy systems and new kind of loads integration

Conventional transformers can integrate PV or wind generation systems into the grid. Their electromagnetic characteristic significantly impacts PQ, especially during low radiation and wind speed periods in weak grids. This operating scenario is translated into a low active power injection by the renewable generating units and makes the magnetizing transformer currents considerable with respect to load currents. The generated harmonics by this phenomenon mainly depend on the winding connection type and the harmonic content presented on the grid voltage [70].

Fig. 1.9(d) shows the presented scenario employing an HDT, which uses the configuration of Fig. 1.4(j). It allows for attenuating the impact of the renewable systems on the power electric system through an appropriate control system, which accounts for the transformer currents in the model. By doing this, the grid current on the MV side

1.6. Thesis motivation Chapter 1

is proportional to the current injected by the renewable generating units for all radiation and wind speed ranges. Additionally, it is possible to design the controllers to operate with unit PF if the converter rating allows it [70].

New kinds of loads, such as electric vehicles, can produce additional stress on distribution transformers, for instance, during multiple charging processes occurring in the evening and night-time, especially at the domiciliary level [16]. Using an HDT, as exemplified in Fig. 1.9(e), can benefit the LFT lifetime, as the power converter can dampen the power consumption and avoid overloading the LFT.

# 1.5.5 Decentralized control of an HDT for voltage regulation in active grids

Expanding the use of distributed generation represents a challenge for the planning of distribution grids. One of the main concerns is the effect of the intermittence of renewable sources, which for example impacts the voltage profile of the distribution grid. Therefore, using smart devices and new control techniques is required to cope with these challenges.

Active Distribution Networks (ADNs) can take advantage of HDTs in order to improve the voltage profiles. For example, the HDT configuration of Fig. 1.4(e) can provide voltage control to the LV side by means of the series converter. On the other hand, the power converter connected to the AW can absorb/inject a limited amount of reactive power, which, in conjunction with other HDTs or smart devices, can provide voltage regulation to the MV buses.

Multiple HDTs, as shown in Fig. 1.9(f), can be coordinated to regulate the voltage magnitude of the MV buses while optimizing the reactive power injection/consumption of the HDTs. This task can be done in a decentralized manner, utilizing HDTs controlled with local variables exclusively [83].

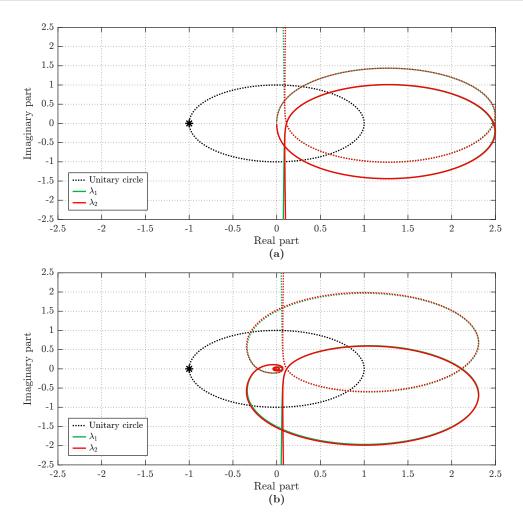

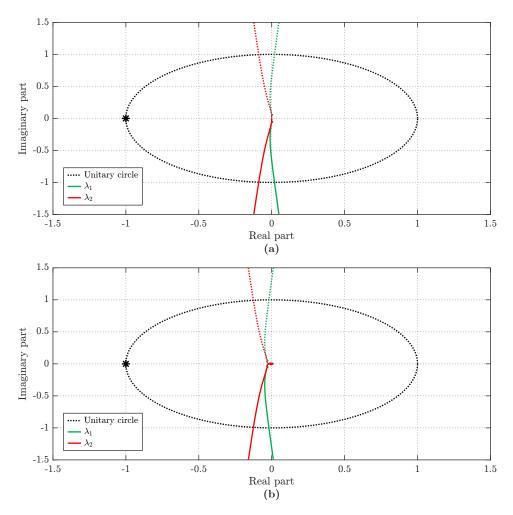

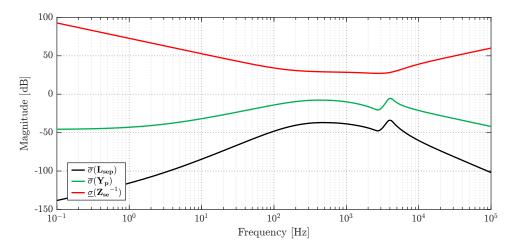

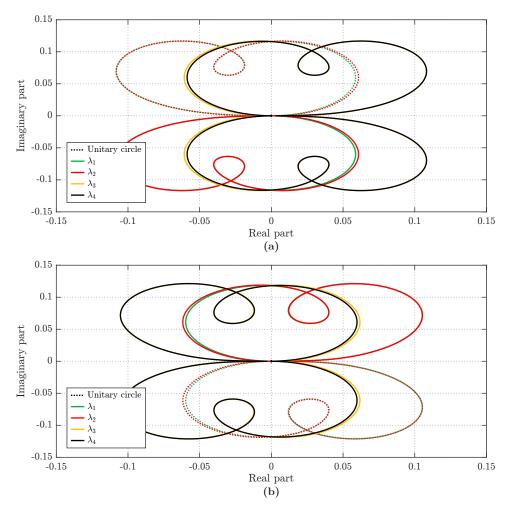

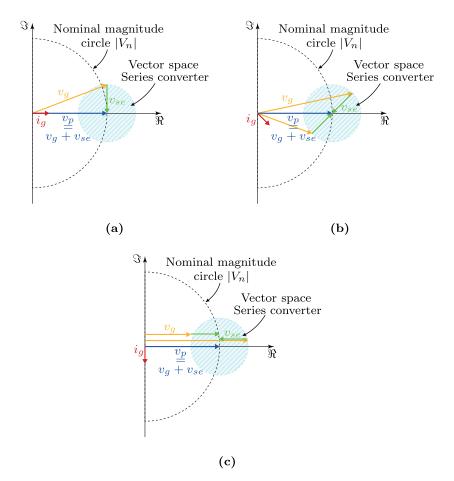

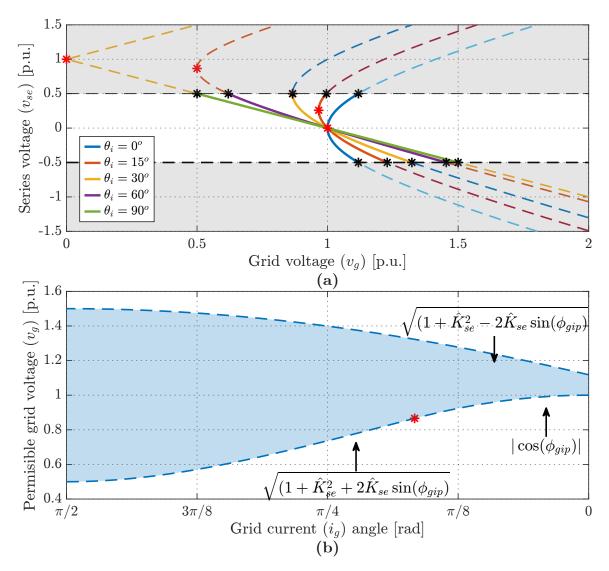

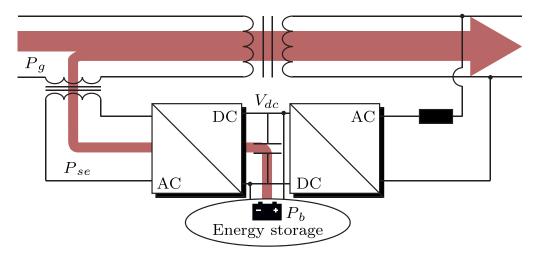

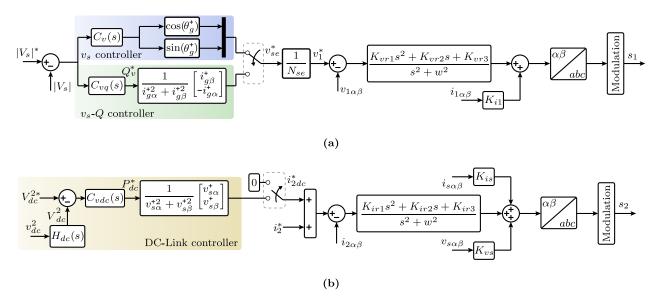

#### 1.6 Thesis motivation